基于NIOSⅡ的GPS信息接收系統(tǒng)設(shè)計與實現(xiàn)

摘要:全球衛(wèi)星定位系統(tǒng)(CPS)可以時海陸空進行全方位的實時定位與導(dǎo)航,其應(yīng)用日益廣泛,通過GPS定位系統(tǒng)及其信息接收裝置可以實現(xiàn)對當(dāng)前所在位置的確定 系統(tǒng)使用天線接收GPS衛(wèi)星信號,并在μC/OS操作系統(tǒng)下用NIOS處理器進行分析處理,以保證其實時性,最終輸出位置、速度等信息進行定位。本系統(tǒng)通過實驗測試驗證,定位具有較高的準確性和實時性。

關(guān)鍵詞:GPS;衛(wèi)星定位;NIOS處理器;μC/OS操作系統(tǒng)

0 引言

GPS全球衛(wèi)星定位系統(tǒng)在天空中是由24顆衛(wèi)星組成的GPS星座構(gòu)成,它們特定的排列方式可以使地球上任何地方任何時刻都可以觀測到四顆及以上衛(wèi)星,定位精度高,是現(xiàn)有的衛(wèi)星定位系統(tǒng)中最常用的技術(shù)比較成熟和穩(wěn)定的定位系統(tǒng),因此在當(dāng)今社會GPS的應(yīng)用十分廣泛,涵蓋陸地、海洋以及航空航天方面的應(yīng)用,尤其是車輛導(dǎo)航、航程航線測定、船只實時調(diào)度與導(dǎo)航等都可以看成是一個個GPS顯示系統(tǒng)。可見,GPS顯示系統(tǒng)能為人們的生活和工作帶來許多方便,所以GPS信息接收和顯示裝置的設(shè)計開發(fā)具有廣闊的發(fā)展前景。

GPS信息的接收模塊技術(shù)如今比較成熟,主要可以分為軍事和民用的兩類。民用的GPS芯片對于精度的要求并不是很高,但基本都能滿足人們的實用要求。由于GPS模塊接收到的數(shù)據(jù)無法直接讀取,因此需要設(shè)計一個合理的信息接收轉(zhuǎn)換及顯示系統(tǒng),將GPS模塊接收的定位數(shù)據(jù)轉(zhuǎn)化為能夠直接讀取的格式并顯示出來。

本文設(shè)計的基于NIOS處理器的GPS定位信息顯示系統(tǒng)的主要目的是接收GPS定位衛(wèi)星的定位信息并實現(xiàn)時間、經(jīng)度、緯度以及速度等信息的實時顯示,為人們的日常生活帶來便利。

1 系統(tǒng)的原理及整體設(shè)計

1.1 系統(tǒng)原理

GPS模塊接收GPS定位衛(wèi)星發(fā)射的信號,并在其內(nèi)部經(jīng)過一系列的信息處理解析出具有一定格式的、可讀性較強的導(dǎo)航電文,其中包含了經(jīng)緯度和速度等定位信息。系統(tǒng)設(shè)計的GPS信息接收系統(tǒng),主要是基于FPGA完成的,通過Verilog硬件描述語言在FPGA上嵌入NIOSⅡ處理器,并引入μC/OS實時操作系統(tǒng)來優(yōu)化整個系統(tǒng)的工作,通過C語言編程從GPS模塊輸出的定位信息中提取經(jīng)緯度和速度等信息,并利用液晶顯示器顯示出來。

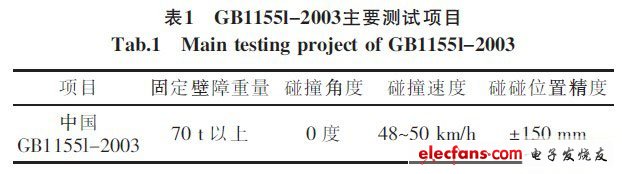

GPS的輸出數(shù)據(jù)遵循NMEA-0183協(xié)議標準,即美國海軍的電子設(shè)備標準。該協(xié)議定義了GPS接收模塊輸出的標準信息,最常用、兼容性最廣的語句格式包括:$GPRMC,$GPGGA,$GPGSV,$GPGSA,$GPGLL等。本設(shè)計選用$GPRMC,其數(shù)據(jù)格式為:

$GPRMC,1>,2>,3>,4>,5>,6>,7>,8>,9>,10>,11>,12>*hh

其中:1>為格林尼治時間;2>為定位狀態(tài),A=有效定位;3>為緯度;4>為緯度半球;5>為經(jīng)度;6>為經(jīng)度半球;7>為地面速率;8>為地面航向;9>為格林尼治日期。

1.2 系統(tǒng)整體設(shè)計

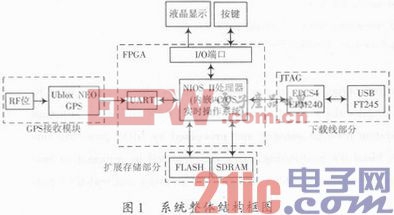

系統(tǒng)總體分為五大部分:GPS接收模塊、FPGA及其內(nèi)部NIOSⅡ處理器部分、擴展存儲部分、液晶顯示部分及下載線部分。其整體結(jié)構(gòu)框圖如圖1所示。

(1)GPS接收模塊。能夠捕獲到按一定衛(wèi)星高度截止角所選擇的待測衛(wèi)星的信號,并跟蹤這些衛(wèi)星的運行,對所接收到的GPS信號進行變換、放大等處理,測出GPS信號從衛(wèi)星到接收機天線的傳輸時間,從而解譯出GPS所發(fā)送的導(dǎo)航電文。此過程完全在現(xiàn)有的GPS模塊中完成,本設(shè)計只需要了解其輸出數(shù)據(jù)的格式并完成對它的解析即可。

(2)FPGA及其內(nèi)部NIOSⅡ處理器部分。通過使用Verilog硬件描述語言在FPGA上搭建一個MOSⅡ處理器,并描述出FPGA內(nèi)部邏輯電路的連接方式,然后在NIOSⅡ處理器中移植入一個μC/OS操作系統(tǒng),采用C語言編程控制整個系統(tǒng)的工作,對GPS導(dǎo)航電文進行解析并控制液晶顯示等。

(3)擴展存儲部分。片外的FLASH和SDRAM擴展了系統(tǒng)的容量,可以實現(xiàn)大規(guī)模的編程,完成復(fù)雜的任務(wù),本設(shè)計由于需要操作系統(tǒng)的植入,需要更大的存儲空間,因此在FPGA的外圍設(shè)置了FLASH和SDRAM。

(4)液晶顯示部分。FPGA將從GPS模塊解析出來的位置、速度等信息送給液晶,由液晶顯示器顯示出來,并且要保證其能夠?qū)崟r更新。

(5)下載線部分。通過Altera USB Blaster把電腦里編譯好的程序下載到FPGA中的NIOSⅡ處理器上,并進行在線調(diào)試。

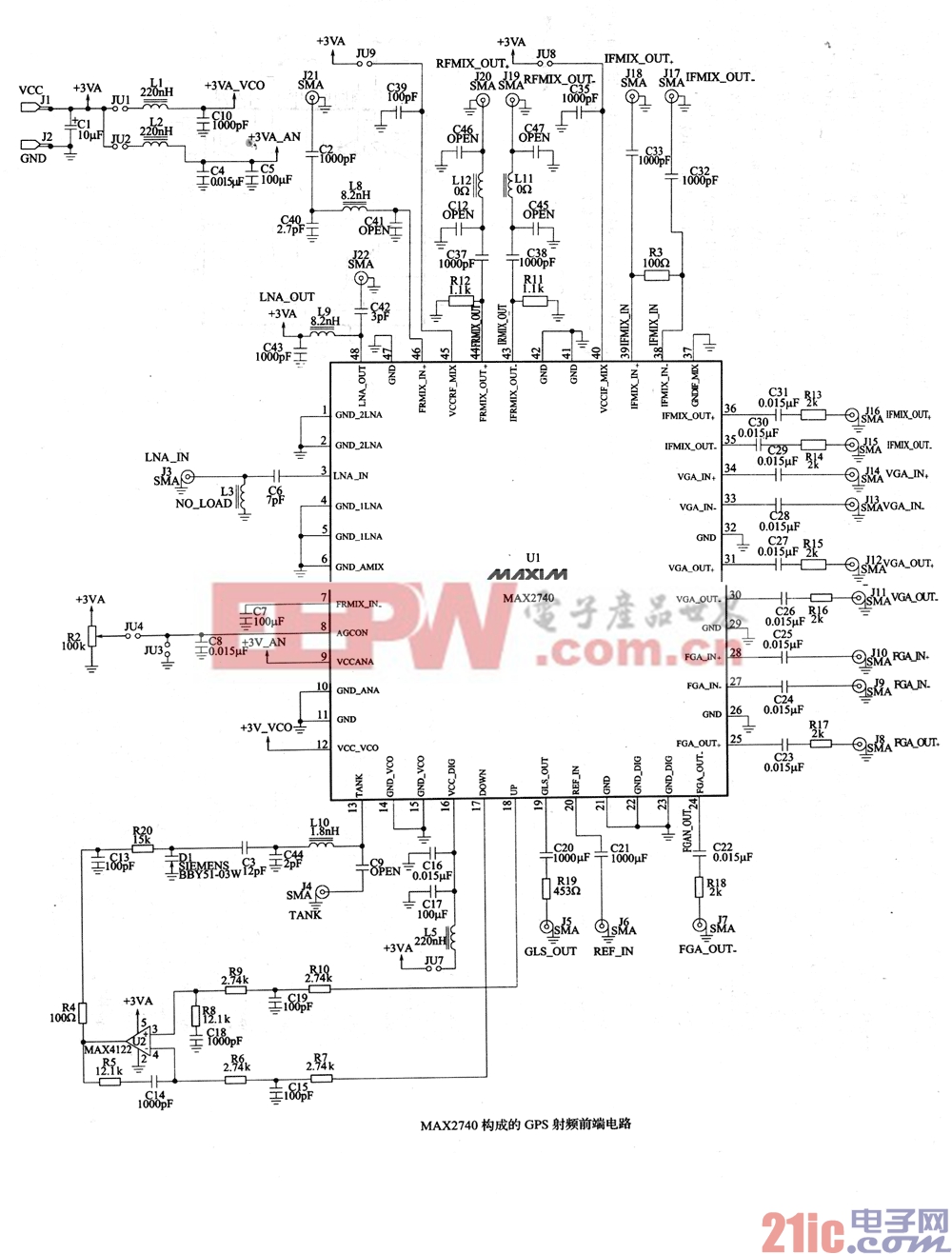

2 系統(tǒng)硬件設(shè)計

系統(tǒng)硬件設(shè)計根據(jù)各部分的功能需求主要包括2個部分:FPGA及其外圍電路、GPS模塊及液晶顯示電路。GPS模塊負責(zé)接收衛(wèi)星的定位信息并輸出導(dǎo)航電文,F(xiàn)PGA及其嵌入的NIOS處理器是分析和處理導(dǎo)航電文的核心,液晶顯示屏則顯示可直接讀取的定位信息。

2.1 FPCA及其外圍電路

FPGA芯片選用Altera公司的CyeloneⅢ系列芯片,該芯片有相應(yīng)的完善的設(shè)計開發(fā)平臺,方便系統(tǒng)的設(shè)計與調(diào)試。

FPGA配置采用AS+JTAG方式,這樣在調(diào)試階段可以使用JTAG方式,最后當(dāng)程序調(diào)試無誤后在使用AS模式把程序燒到配置芯片里去。這樣做的一個明顯的優(yōu)點是:在AS模式不能下載的時候,可以利用Quartus自帶的工具將配置程序生成.jic文件,用JTAG模式來驗證配置芯片是否損壞。通過JTAG將FPGA的配置程序?qū)懭氲狡馀渲眯酒校綦姴粊G失,每次上電時再將其中的程序讀入到FPGA中。另外在FPGA的I/O引腳接入一些LED燈,方便觀察測試結(jié)果,也可用來檢驗設(shè)計的正確與否。

2.2 GPS接收模塊及液晶顯示電路

GPS接收模塊采用Ublox NEO-6M模塊,它是一個現(xiàn)有的GPS接收模塊,輸出的導(dǎo)航電文格式清晰,便于處理。它將接收到的衛(wèi)星定位信息在其內(nèi)部經(jīng)過簡單的處理輸出給FPGA的I/O端口,在FPGA內(nèi)部解析之后又通過另外的I/O端口發(fā)送給液晶顯示器。液晶顯示選用12864液晶顯示器,并采用串行數(shù)據(jù)輸入方式,將接收到的數(shù)據(jù)顯示出來。

2.3 供電部分

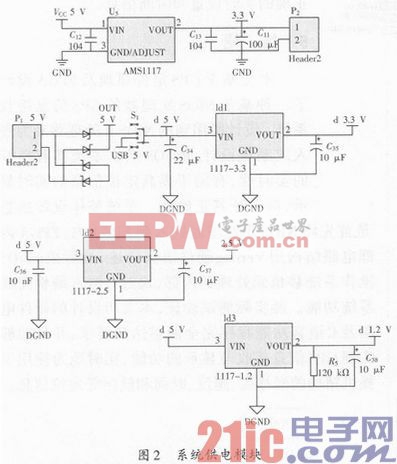

因FPGA各管腳所需輸入電壓包括3.3 V,2.5 V和1.2 V,12864液晶需要5 V,GPS模塊所需電壓為3.3 V,因此整個電路板需要多種供電電壓,供電電路的設(shè)計思想是輸入5 V電壓,再通過電平轉(zhuǎn)換電路轉(zhuǎn)換出其他所需要的電平。

系統(tǒng)供電模塊如圖2所示。其中電源與地之間的電容主要作用是去除電源中耦合的其他信號,以減小甚至是消除這些信號對電源的影響。

評論