頻率合成器的設計

即K0為連續兩次采樣之間的相位增量△ψ,并可得相位序列和K(n)的差分方程

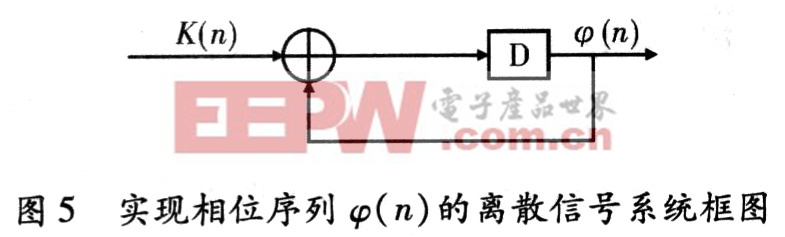

ψ(n)-ψ9(n-1)=K(n-1)

其系統模型,如圖5所示,這是以K(n)為激勵序列,ψ(n)為響應序列構成的一個離散信號系統,這是一個線性系統。不難看出相位序列的實現過程實質上是一個相位增量K0進行線性累加的過程。本文引用地址:http://www.104case.com/article/188494.htm

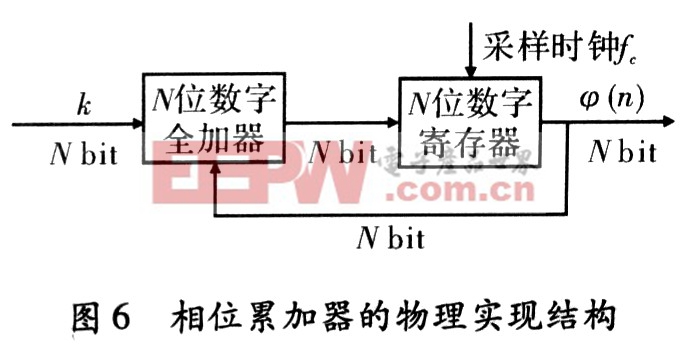

在工程實踐中,可采用相位累加器來實現上述的相位累加過程。相位累加器結構,如圖6所示,它用N位數字全加器和Ⅳ位數字寄存器構成,K為輸入參數,用以改變每次累加的相位增量。

相位累加器的工作過程為:每當一個采樣時鐘脈沖到來時,加法器就將輸入參數K與寄存器輸出的數據相加,相加后的結果再送至寄存器。當相位累加器累積滿量時,就會產生一次溢出,從而完成一個周期性的累加動作。由相位累加器的值所構成的相位序列可表示為

在相位累加器中,如果采用N位字長的數字寄存器來存儲正弦波形一個周期內的抽樣后的離散相位,這實際上是對[0,2π]的相位區間進行N位字長的線性量化,其等效結果是使輸入參數K和相位增量K0之間建立了一個一一映射的關系

累加器的累加周期即是DDS合成信號的一個頻率周期,其值為2N/K個時鐘周期。因此合成信號的頻率為

這就是DDS輸出信號的頻率關系表達式,在一定的時鐘頻率之下,K決定了合成信號的頻率,故K被稱為頻率控制字。

從以上分析不難看出,K也決定了每次累加的相位增量。例如,K=1,其采樣相位增量K=2,則K越大,每個時鐘周期抽樣跨越的相位越大,相位累加器的溢出所需時鐘脈沖的個數越少,也即DDS合成信號的頻率越高。由此可見,在一定頻率的時鐘信號作用下,改變每次累加的相位增量,即能改變DDS信號頻率。

在得到頻率為f0的余弦信號量化的數字的相位序列ψ(n)之后,接著需要實現的是數字相位序列到幅度序列f(n)的轉化。根據式(4)和式(5),相位序列ψ(n)和幅度序列f(n)之間有著確定的對應關系。如果將這對應關系固化在一個只讀存儲器(ROM)中,并且以ψ(n)作為只讀存儲器的存儲單元的地址,而量化后的正弦波形幅度序列f(n)是存儲單元的內容。那么,當以相位累加器輸出的相位序列ψ(n)對只讀存儲器尋址時,存儲器的輸出即為幅度序列f(n)。由f(n)即可構造fs(t),進而得到f(t)實現DDS。

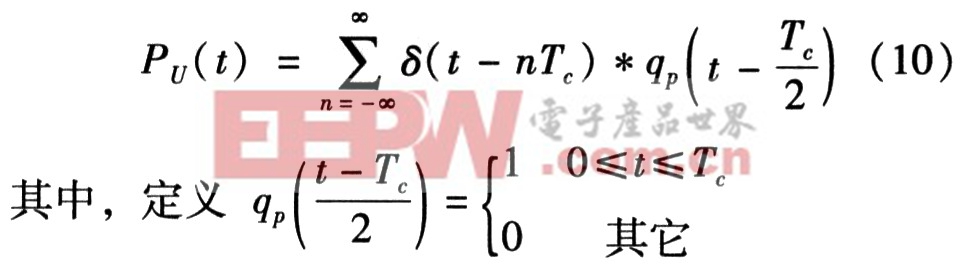

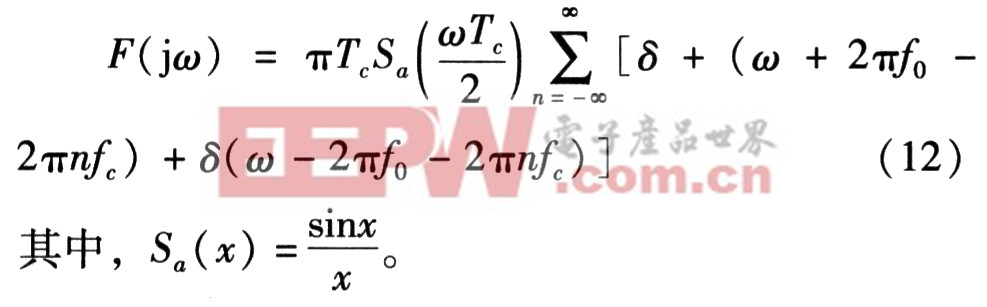

這里需要說明的是,在實際工程中,單位沖激函數是很難實現的,實際抽樣往往采用脈沖串函數,其表達式如下

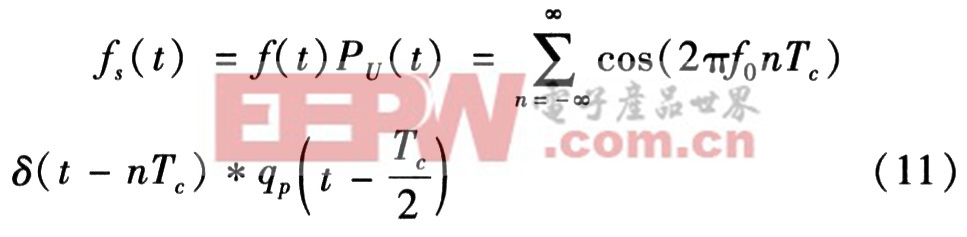

由此可得抽樣函數為

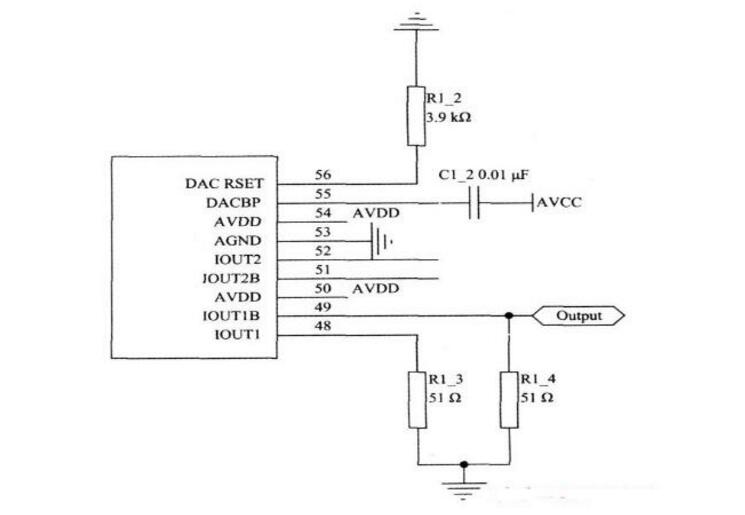

與式(3)相比,式(12)多一個幅度加權項 但仍包含f(t)的全部信息,經過理想低通濾波器仍能恢復原始信號f(t),只是幅度有所變化。于是,在物理實現f(n)的基礎上,使之通過一個數模轉換器(DAC),便可構造一個如式(11)所表示的抽樣函數fs(t)。再通過低通濾波器濾除高頻分量便可得到余弦波形,即實現了DDS。

但仍包含f(t)的全部信息,經過理想低通濾波器仍能恢復原始信號f(t),只是幅度有所變化。于是,在物理實現f(n)的基礎上,使之通過一個數模轉換器(DAC),便可構造一個如式(11)所表示的抽樣函數fs(t)。再通過低通濾波器濾除高頻分量便可得到余弦波形,即實現了DDS。

4 結束語

從上述分析可以看出,使用DDS方法設計的頻率合成器具有硬件簡單、輸出頻率穩定度高等特點。隨著半導體技術的發展,基于上述DDS理論的軟件頻率合成會越來越多的出現在現代接收設備的設計中。

評論