基于折疊結構的半帶濾波器的設計

3 仿真與實現本文引用地址:http://www.104case.com/article/187587.htm

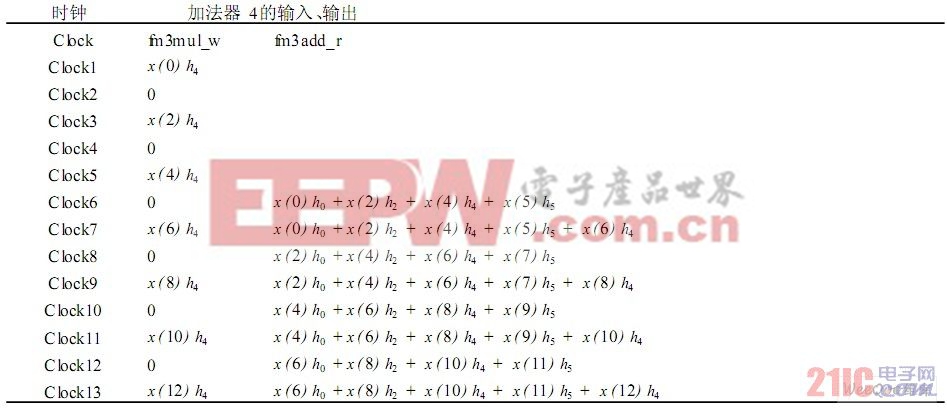

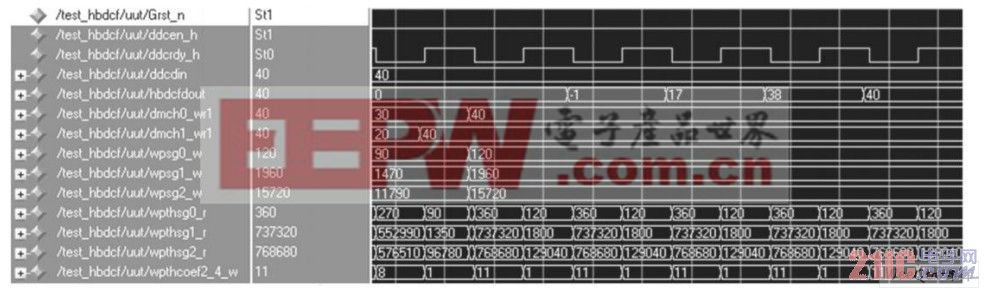

本設計采用Verilog語言編寫,所采用的芯片是Xilinx公司的xc4vsx35 - 10ff668,用ISE10. 1和Modelsim進行仿真驗證。仿真結果、綜合報告圖如圖3、圖4所示。從圖3我們可以看出采用折疊技術的半帶濾波器,其系數的產生以及最終濾波器的輸出完全正確,完全滿足我們的設計要求。

傳統的直接型半帶濾波器的設計單單濾波過程,不包括系數的產生和抽取過程,需要10個D觸發器、7個乘法器、6個加法器,而轉置型半帶濾波器則需要10個D 觸發器、4 個乘法器、7 個加法器。

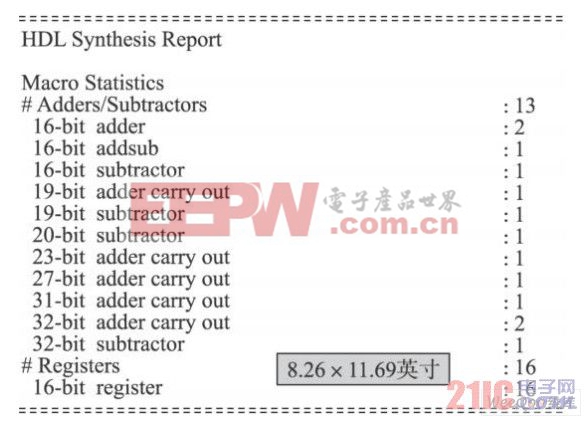

然而從圖4我們可以看到整個半帶濾波器耗費的資源相當的少,總共用了13 個加法器, 16 個寄存器。而由此可見采用折疊結構實現半帶濾波器的設計能夠大大減少資源的耗費,而且整個過程沒有用到乘法器只是用到少量的加法器和寄存器,減少了大量的乘法帶來的額外的面積和功耗。同時本設計還經過硬件電路的驗證,工作正常穩定,符合設計要求。

圖3 基于折疊結構的11階半帶濾波器仿真圖

圖4 基于折疊結構的11階半帶濾波器綜合報告圖

4 結論

本文以11階半帶濾波器的設計為例,介紹了折疊技術在半帶濾波器上的應用。與傳統的設計相比其有很大的優越性和突破,單一時鐘控制,并且設計過程當中沒用到乘法器,大大減少了硬件資源,同時也使設計面積和功耗大為減少,穩定性高!

評論