一種帶有增益提高技術的高速CMOS運算放大器設計

2 仿真結果

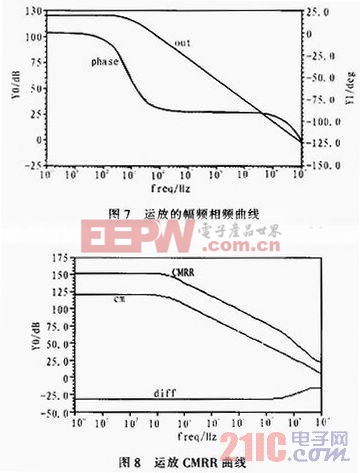

采用SMIC 0.25μm CMOS工藝模型,在Cadence環境下對電路進行Spectre仿真,2.5 V單電源供電,模擬結果顯示:運放的直流增益為124 dB,單位增益帶寬為720 MHz,相位裕度64°CMRR高達153dB。本文引用地址:http://www.104case.com/article/186166.htm

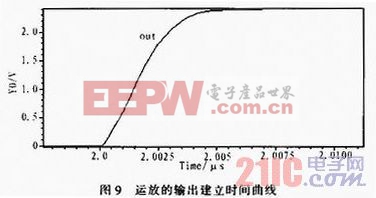

運放的瞬態建立特性如圖9所示,于輸入端2μs處加2.5 V的階躍響應,由輸出波形測得轉換速率885 V/μs;達到0.1%的穩定精度的建立時間為4ns。

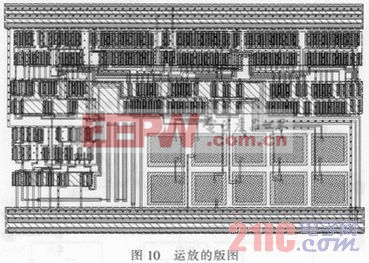

圖10是運算放大器的版圖,通過了DRC與LVS驗證,結果顯示性能良好。

3 結論

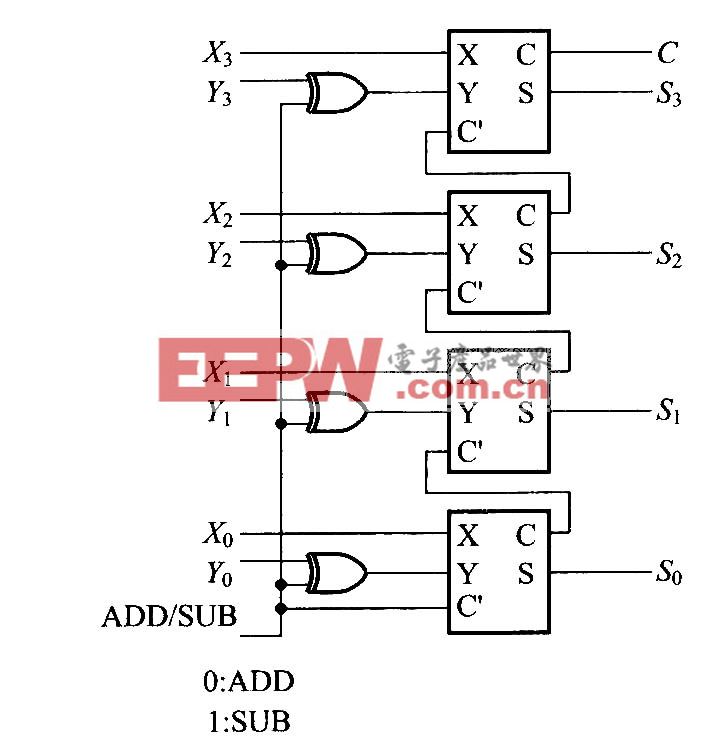

文中提出了一種可用于高速Pipelined ADC中的前置放大器,結合開關電容共模反饋與三支路共源共柵基準電流源等技術,詳細分析了增益提高技術的設計原理、弊端及改進方法,實現了一個全差分帶增益提升級的折疊式CMOS運算放大器。仿真結果表明:該運放的直流增益達到124 dB,單位增益帶寬720 MHz,達刮0.1%精度建立時間為4 ns,轉換速率高達885 V/μs。性能良好,滿足系統設計要求。

評論