在DC/DC設計中優化同步降壓器的挑戰

案例1

相位節點上的振蕩或振鳴會產生兩種負面影響。振蕩期間的峰值電壓會超過MOSFET數據表中VDSS最大值的80%,這是工程人員考慮可靠性時應遵守的典型準則。振鳴是輻射和傳導信號的來源,會在敏感的數字線路上產生噪聲,或使系統無法通過EMI測試。

針對以上問題的解決方法如下:

1.同時減緩高邊FET電壓的上升和下降速度 (添加R1)

2.只減緩高邊FET電壓的上升速度 (添加Rboot)

3.降低施加在高邊FET柵極上的驅動電壓 (添加C1或降低VCC)

4.降低施加在低邊FET柵極上的驅動電壓 (降低VCC)

5.減小低邊FET的回路面積,以降低回路電感 (LDRV 到 PGND的回路)

6.選擇先進的MOSFET封裝以減少寄生電感,Lp = Lss + Ldd

7.選擇具有較低Qrr值的MOSFET;該Qrr值是 Coss的一部分,并對Cp有貢獻

要降低HDRV引腳的驅動電壓,C1約等于Cboot / 5 是很好的起步點。可串聯兩個升壓二極管來降低VCC,進而降低驅動電壓。要降低LDRV到PGND回路的電感,可讓驅動器靠近低邊晶體管。要減小低邊FET源極 (Ldd) 到 PGND的回路電感,可在PGND 銅層和源極間增設近路連接。

可根據MOSFET (封裝和獨立的器件特性) 和線路布局,決定使用以上任何組合。

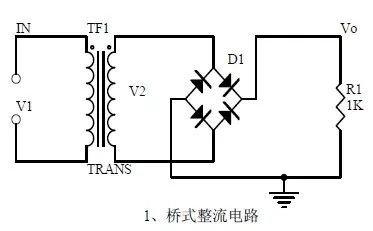

圖1同步降壓等效電路

如圖1所示,HDRV電壓降低太多,在HDRV引腳電壓之上的開關節點信號會引起高邊晶體管的柵-源電壓下降,在此期間出現一次或多次低于Vgs(th) 的情況,就會帶來更高的開關損耗,降低效率。

圖2 Q1導通和Q2關斷時的升壓過渡

圖3 導通波形,其中t1 到 t3

間產生開關損耗

從圖2和圖3可以看出:Q1不只一次穿過有源區 (t2-t3) 以及阻抗區 (t4-t5)。這意味著高邊晶體管產生了額外的開關損耗。通過減小或省掉C1來增加HDRV電壓,可降低這個額外的開關損耗。

當上述措施無效時,通常會采用RC 緩沖電路。RC緩沖電路 (即圖1中Rs 和 Cs組成的電路) 可按如下步驟實現:

1.在未添加RC 緩沖電路的降壓器上加入負載。探測開關節點或低邊MOSFET,直到觀察到共振,找出開關節點上升沿的共振頻率 (fo1)。在測量開關節點時,應在探針上使用短線接地引腳,以便將回路電感引起的錯誤減至最少。

ωo1 = 2πfo1 = [1]

2.在低邊FET的漏極到源極間跨接一個電容(Cadd),然后再重新確定共振頻率 (fo2)。

ωo2 = 2πf o2 = [2]一旦獲得 fo1 和 fo2 ,就可導出Cadd 和Cp間的關系。可以驗證如下的關系:

fo1 / 2 = fo2 ; Cadd = 3Cp [3]

fo1 x 0.75 = fo2 ; Cadd = (9/7) Cp [4]

MOSFET數據手冊一般都不包含引腳電感值。PSPICE仿真模型并不能反映真實的布線電感。建議在確定Cp后,用方程 1 來計算Lp。

3.為了使RC緩沖電路具備臨界阻尼響應性能,應恰當選取Rs。可根據串聯RLC電路的自然響應性能方程來確定Rs,即:

Q = [5]

Q = 1;臨界阻尼響應

Q > 1;欠阻尼響應性能-希望緩沖電路超前響應Lp、Cp 振蕩

Q < 1;過阻尼響應性能-希望緩沖電路滯后響應Lp、Cp 振蕩

可選用Q=1時計算出來的Rs值。調整Rs可在開關節點上獲得所希望的阻尼電平。

4.許多關于緩沖電路的文獻建議Cs ≥ 2Cp,但這會在Rs上產生額外且難以接受的功率損耗。根據平均功率損耗公式 (參見步驟5),Cs的選擇顯然是影響功率損耗的重要因素。因此,對于重視效率的設計,必須進行折中,即取Cp < Cs < 2Cp。

5.在選取Rs的額定功率時,可考慮Cs在充電和放電周期中存儲的峰值能量。

w = (Cs Vin2) / 2

wtotal = (Cs Vin2)

由于能量隨時間變化,平均功率損耗應為:

Pd ~ Cs Vin2 fsw [6]

6.如果第1至第5步的措施還不能抑制振蕩,就需要檢查輸入濾波電路的穩定性。根據R.D. Middlebrook發表的文獻摘要,若下式成立,則可實現穩定性或非振蕩條件:

[7]

這里,D = Vout/Vin ,方程 7 降低了輸入L和C電路共振頻率附近的Q值。

案例2

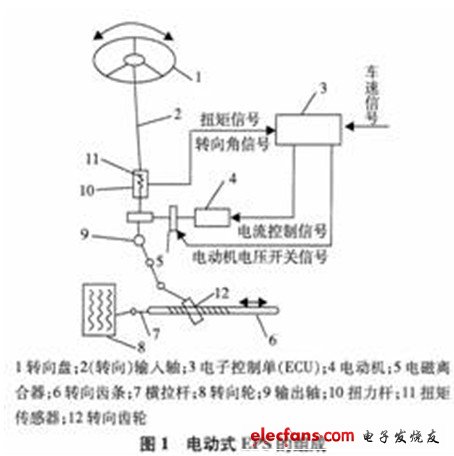

高于低邊晶體管閾值Vgs的柵極沖擊電壓會造成低邊和高邊FET同時導通。這會在每個開關循環產生重復性短路。雖然每個循環的交叉導通時間只有5~10ns,但時間一長便會導致熱失控,使FET超過其最大允許結溫。在相位節點上的大電壓變化dv/dt、Cgd 和Cgs電容比值、Qrr及驅動電路的反偏阻抗都會產生柵極沖擊電壓。

MOSFET驅動器中的自適應柵極驅動電路能夠大幅縮短死區時間,同時防止潛在的交叉導通電流。當高邊和低邊晶體管同時導通時,會建立一個從輸入電壓端到地的低阻抗信道,通常,這會對采用較小芯片的高邊晶體管形成較大的應力 (選用較小的芯片是為了將開關損耗減至最少)。相比采用較大芯片的低邊晶體管,采用較小芯片的高邊晶體管會先達到功率耗散限度。自適應柵極驅動電路雖然是智能化的,但它只能從HDRV、LDRV和開關引腳獲取電壓信息,從而做出開關轉換的決定。由于不能讀取內部VGS,因此它不知道晶體管是否完全導通或關斷。此外,下面的因素也進一步限制了自適應柵極驅動電路防止交叉導通的能力。

圖4 N信道MOSFET的等效電路

當低邊晶體管出現電壓變化 (dv/dt) ,將會產生兩個電流通道。在圖4中,沿信道 (a) 的電流在晶體管內部柵極產生額外的Vgs。

Igs = Cgd dv/dt [8]

Igs = Vgs / Zgs [9]

τ= Zgs (Cgd + Cgs)

這里,Zgs=下拉電阻 + HDRV 和MOSFET柵極間的外接電阻 + MOSFET內部柵極電阻。

v(t) = Vin-Vin

評論