MOSFET柵漏電流噪聲模型研究

CMOS器件的等比例縮小發(fā)展趨勢(shì),導(dǎo)致了柵等效氧化層厚度、柵長(zhǎng)度和柵面積都急劇減小。對(duì)于常規(guī)體MOSFET,當(dāng)氧化層厚度2 nm時(shí),大量載流子以不同機(jī)制通過柵介質(zhì)形成顯著的柵極漏電流。柵極漏電流不僅能產(chǎn)生于溝道區(qū)域,而且能在柵極與源/漏的交疊區(qū)域產(chǎn)生。穿越柵氧化層的電流增加了電路的泄漏電流,從而增加了電路的靜態(tài)功耗,同時(shí)也影響MOS器件的導(dǎo)通特性,甚至導(dǎo)致器件特性不正常。柵漏電流增加成為器件尺寸縮減的主要限制因素之一。

柵氧化層越薄,柵漏電流越大,工藝偏差也越大。柵漏電流噪聲一方面影響器件性能,另一方面可用于柵介質(zhì)質(zhì)量表征,因此由柵介質(zhì)擊穿和隧穿引起的柵電流漲落為人們廣泛關(guān)注。為了更好地描述和解釋柵電流漲落對(duì)MOS器件性能的影響,迫切需要建立柵漏電流噪聲精確模型。MOS器件噪聲的研究,始于60年代,至今已有大量研究報(bào)道文獻(xiàn)。而柵漏電流大的MOS器件噪聲特性的研究仍是現(xiàn)今研究中活躍的課題。尤其當(dāng)MOS-FET縮減至直接隧穿尺度(3 nm)時(shí),柵漏電流噪聲模型顯得尤為重要,并可為MOSFET可靠性表征和器件設(shè)計(jì)提供依據(jù)。文中基于MOSFET柵氧擊穿效應(yīng)和隧穿效應(yīng),總結(jié)了柵漏電流噪聲特性,歸納了4種柵漏電流噪聲模型,并對(duì)各種模型的特性和局限性進(jìn)行了分析。

1 柵漏電流噪聲模型

(1)超薄柵氧隧穿漏電流低頻噪聲模型。

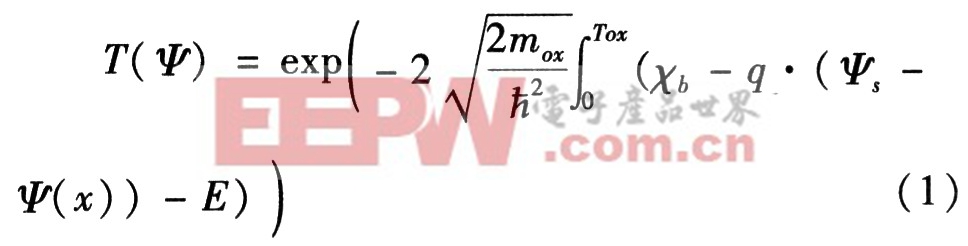

模型基于泊松方程與薛定諤方程自洽數(shù)值求解,采用一維近似描述了器件的靜態(tài)特性,模型考慮了柵材料多晶硅耗盡效應(yīng)和量子力學(xué)效應(yīng)。在描述超薄氧化層的柵漏時(shí),同時(shí)考慮了勢(shì)壘透射和界面反射,電子透射系數(shù)表達(dá)式為

其中,χb為勢(shì)壘高度,ψ(y)為位置y處的電勢(shì),E為隧穿電子能級(jí)。

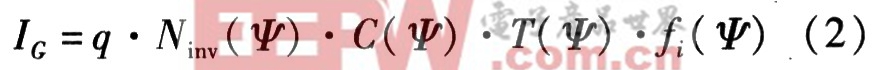

總柵隧穿電流為

其中,Ninv(ψ)為反型層電荷,C(ψ)為取決于界面反射的修正系數(shù),fi(ψ)為頻率因子。

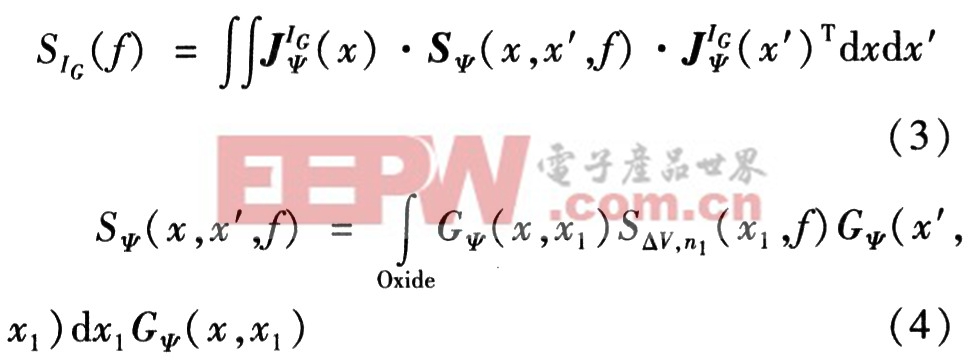

氧化層內(nèi)部的缺陷對(duì)柵漏電流漲落的貢獻(xiàn),已在格林表達(dá)式中考慮和體現(xiàn)。這種近似允許擯棄等效平帶電壓漲落的假設(shè),由此得到的柵電流漲落譜密度為

其中,![]() 為與靜電勢(shì)ψ(y)相關(guān)的柵電流,IG的雅可比矩陣,Gψ(x,x1)為氧化層x1處的單位電荷在氧化層x處的電勢(shì)ψ(x)的格林函數(shù)。

為與靜電勢(shì)ψ(y)相關(guān)的柵電流,IG的雅可比矩陣,Gψ(x,x1)為氧化層x1處的單位電荷在氧化層x處的電勢(shì)ψ(x)的格林函數(shù)。

基爾霍夫電流相關(guān)文章:基爾霍夫電流定律

評(píng)論