高速PCB中旁路電容的分析

3 利用電容模型分析PCB中的環(huán)流問(wèn)題

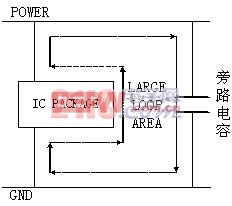

電源去耦電容放置位置不當(dāng)將會(huì)在印制電路板上產(chǎn)生很大的電流環(huán)。為了減少噪聲,在高速印制電路板的設(shè)計(jì)當(dāng)中,有一個(gè)很重要的原則是:減少信號(hào)電流環(huán)的面積。過(guò)去我們習(xí)慣于只考慮電流的流出起點(diǎn)、途徑及終點(diǎn),而很少去考慮電流的返回路徑。在高頻電路中,通常認(rèn)為電源和地是等價(jià)的,因此電流的流出途徑和返回途徑將形成一個(gè)電流環(huán),在這些電流環(huán)中,會(huì)由于種種原因,例如電容的寄生電感,PCB連線的固有電感等,使得環(huán)路的阻抗不為零,這樣電流流經(jīng)這一環(huán)路時(shí)將產(chǎn)生電勢(shì)差,如果電流是變化的,則將產(chǎn)生輻射,對(duì)系統(tǒng)產(chǎn)生干擾。為了給電源濾波,在電路設(shè)計(jì)中常常要在電源和地之間加上一些旁路電容,在回路中增加旁路電容主要有兩個(gè)目的,一是增加環(huán)路中存儲(chǔ)電荷的能力,以免瞬間電流過(guò)大,產(chǎn)生地彈噪聲。二是適當(dāng)?shù)姆胖?a class="contentlabel" href="http://www.104case.com/news/listbylabel/label/旁路">旁路電容的位置,可為噪聲信號(hào)提供就近的地回路,減少電流環(huán)路的面積,從而減少了環(huán)路的電感。采用了旁路電容的回路中,由于欲濾除的噪聲頻率通常是高頻交流信號(hào),因而這樣的回路仍舊將會(huì)對(duì)外產(chǎn)生輻射。為了減少這一輻射,我們需要盡可能的降低回路的阻抗,必須合理放置旁路電容的位置。圖4顯示了由于濾波電容放置位置不當(dāng)產(chǎn)生的大電流環(huán)。

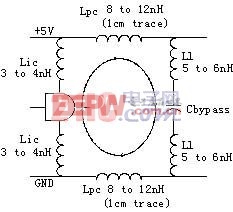

圖5為電流環(huán)的模型。從電流環(huán)模型中我們可以看出,環(huán)路中存在寄生電感,它們?cè)诟哳l狀態(tài)下表現(xiàn)為環(huán)路的阻抗可導(dǎo)致供給電源產(chǎn)生尖峰,并會(huì)輻射電磁波從而干擾系統(tǒng)的其他部分。環(huán)路中Ll為電容管腳引線的封裝電感;Lpc為電容管腳到器件電源或者地管腳之間的PCB傳輸線的寄生電感;Lic為器件管腳引線的寄生電感。另外,在前面我們討論過(guò)電容本身也是具有寄生電感ESL的。這樣回路的總電感為:L=2Ll+ 2Lpc+2Lic+ESL。由于環(huán)路的寄生電感將會(huì)給整個(gè)系統(tǒng)帶來(lái)電磁干擾,產(chǎn)生電壓尖峰,這個(gè)電壓尖峰值同串聯(lián)電感之間存在一定的關(guān)系.

這里V為最大噪聲電壓尖峰值,△t為瞬態(tài)持續(xù)時(shí)間,△I為器件瞬態(tài)電流,△t、△I值可以從器件手冊(cè)中查得。例如74HC的瞬態(tài)電流典型值Icc為20mA,輸出信號(hào)從零上升到Icc或者從Icc下降到零需要的時(shí)間為4ns,如果現(xiàn)在我們?cè)噲D控制感性噪聲的尖峰在100mV以內(nèi),那么由上面的公式我們可以求得串聯(lián)電感L的最大值不超過(guò)20nH。在PCB板設(shè)計(jì)時(shí),設(shè)計(jì)者可以通過(guò)以下幾種方式來(lái)降低回路電感:選擇寄生電感比較小的電容,降低ESL(不同型號(hào)電容的寄生電感值見(jiàn)表1);盡量使用貼片電容以減小電容引線長(zhǎng),降低Ll值;合理的放置電容,使用電源層或地平面層代替電源或者地傳輸線,減小電源地傳輸線電感Lpc;合理選擇集成器件的封裝,以降低Lic值,比如對(duì)于器件ADV478來(lái)說(shuō),PLCC封裝的寄生電感比DIP封裝的寄生電感要小2nH到3nH。

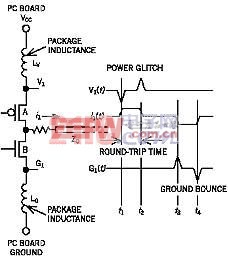

4 電源擾動(dòng)及地彈噪聲的產(chǎn)生機(jī)理

評(píng)論