電源完整性設計1

![]()

這一寄生電感比很多小封裝電容自身的寄生電感要大,必須考慮它的影響。過孔的直徑越大,寄生電感越小。過孔長度越長,電感越大。下面我們就以一個0805封裝0.01uF電容為例,計算安裝前后諧振頻率的變化。參數如下:容值:C=0.01uF。電容自身等效串聯電感:ESL=0.6 nH。安裝后增加的寄生電感:Lmount=1.5nH。

電容的自諧振頻率:

![]()

安裝后的總寄生電感:0.6+1.5=2.1nH。注意,實際上安裝一個電容至少要兩個過孔,寄生電感是串聯的,如果只用兩個過孔,則過孔引入的寄生電感就有3nH。但是在電容的每一端都并聯幾個過孔,可以有效減小總的寄生電感量,這和安裝方法有關。

安裝后的諧振頻率為:

![]()

可見,安裝后電容的諧振頻率發生了很大的偏移,使得小電容的高頻去耦特性被消弱。在進行電路參數設計時,應以這個安裝后的諧振頻率計算,因為這才是電容在電路板上的實際表現。

安裝電感對電容的去耦特性產生很大影響,應盡量減小。實際上,如何最大程度的減小安裝后的寄生電感,是一個非常重要的問題,本文后面還要專門討論。

局部去耦設計方法

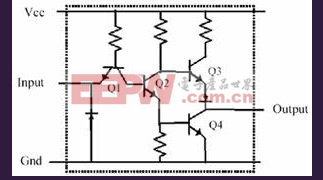

我們從一個典型邏輯電路入手,討論局部退耦設計方法。圖7是典型的非門(NOT GATE)電路。當輸入(Input)低電平時,Q1打開,拉低Q2的基極,因此Q4的基極被拉低,Q3打開,輸出(Output)高電平。

圖7 非門內部邏輯

實際電路設計中,器件之間相互連接構成完整系統,因此器件之間必然存在相互影響。作為例子,我們級聯兩個非門,如圖8所示,看看兩個器件之間怎樣相互影響。理想的情況應該是:第一個非門輸入邏輯低電平(邏輯0),其輸出為高電平,第二個非門輸入為第一個的輸出,也為高電平,因此第二個非門輸出低電平。

為保證邏輯電路能正常工作,表征電路邏輯狀態的電平值必須落在一定范圍內。比如對于3.3V邏輯,高電平大于2V為邏輯1,低電平小于0.8V為邏輯0。當邏輯門電路的輸入電平處于上述范圍內時,電路能保證對輸入邏輯狀態的正確判斷。當電平值處于0.8V到2V之間時,則不能保證對輸入邏輯狀態的正確判斷,對于本例的非門來說,其輸出可能是邏輯0,也可能是邏輯1,或者處于不定態。因此輸入電平超出規定范圍時,可能發生邏輯錯誤。

邏輯電路在設計時采用了很多技術來保證器件本身不會發生這樣的錯誤。但是,當器件安裝到電路板上,板級系統的其他因素仍可能導致類似錯誤的發生。圖8中級聯的兩個非門共用電源端Vcc和接地端GND。Vcc到每個非門供電引腳間都會存在寄生電感,每個非門的地引腳到GND之間也同樣存在寄生電感。在實際板級電路中設計中,寄生電感不可避免,電源平面、地平面、過孔、焊盤、連接焊盤的引出線都會引入額外的寄生電感。圖8已經畫出了電源端和地端的寄生電感。當第一個非門輸入高電平,其輸出低電平。此時將會形成圖中虛線所示的電流通路,第一個非門接地處寄生電感上的電壓為:V=L*di/dt。這里i為邏輯轉換過程形成的瞬態電流。如果電路轉換過程非常快(高速器件內部晶體管轉換時間已經降到了皮秒級),di/dt將是個很大的值,即使很小的寄生電感L也會在電感兩端感應出很大的電壓V。對于一些大規模邏輯芯片,接地引腳是內部非常多的晶體管共用的,這些晶體管同時開關的話,將產生很大的瞬態電流,再加上極快的轉換時間,寄生電感上的感應電壓更大。此時第一個非門的輸出信號電平為:非門本身低電平電壓+寄生電感上的電壓。如果這一值接近2V,可能會被第二個非門判斷為邏輯1,從而發生邏輯錯誤。

評論