基于FPGA高速實時數據傳輸系統設計方案

3.3 24bit/16bit數據轉換器的設計 [5] [6]

片外高速數據傳輸芯片為 16位輸入數據總線 [4],而由 fpga內部讀緩沖區讀出的是 24位并行數據,因此需要將 24bit數據轉換成 16bit數據再輸出。考慮到傳送 12個 16bit數據可以等效為 8個 24bit數據,故將數據輸出時鐘 Dclk用一個 0~11的計數器進行計數,然后取其中的 8個連續時鐘讀取 24bit數據,這樣就解決了 16bit數據和 24bit數據在傳輸上時鐘不匹配的問題。讀取的 24bit數據隨后被分成兩個 12bit數據依次裝入 16個 12bit移位寄存器中,再由 Dclk一位一位打出并拼裝成 16bit數據,發送給幀同步產生及高速傳輸芯片控制器進行碼頭加載,將自己編寫的 16bit數據頭校驗碼以及其他一組信息碼插入數據流中輸出給高速數據傳輸芯片,完成整個數據轉換和發送過程。

4.實際測試結果

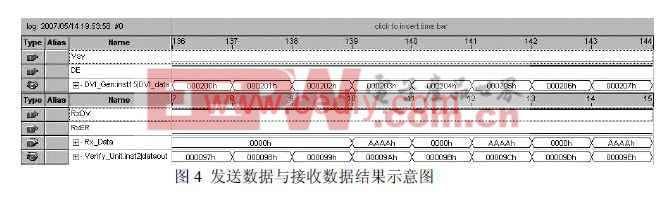

用 TLK1501[4]高速數據傳輸芯片集成的數據接收端口接收其發送端傳輸的高速串行數據流,在芯片內部自解碼之后再恢復成 16bit數據傳給 fpga,通過比對發送數據和接收數據的一致性就可以對邏輯設計、時序等方面進行驗證,以保證設計正確。在實際測試時,用一組設計好的 24bitDVI數據取代實際傳輸的像素信號,而其他同步信號則仍為實際 DVI同步信號,這樣做的目的就是可以對發送數據進行控制,方便與接收數據進行比對,設計的發送數據為一串依次加“1”的規律 24bit數,因此如果接收回的數據信號仍為依次加 “1”的 24bit數,則說明邏輯設計和時序方面沒有問題,設計方案可以用于實際操作中。

圖四上為發送數據波形圖,圖六下為接收數據波形圖。由圖中對比可以看出,接收數據同發送數據均為依次加“1”的 24bit數據,實際測試結果證實整個高速實時數據傳輸系統設計滿足設計要求,可以用于實際操作中。

5.結語

本系統在實際測試中,發送端數據時鐘為 40MHz,由于高速數據傳輸芯片――TLK1501[4]可以傳輸 20倍頻的串行數據流,因此實際在信道中傳輸的數據速度可以達到 800MHz,如此高的傳輸速度可以滿足一般情況下的工程要求,而且本系統由于所選片外存儲器的容量和操作速度上限制,沒能將 TLK1501高速傳輸的特點充分發揮出來,相信在系統改進之后,傳輸速度達到 1G甚至更高的實時數據應該可以實現!

本文作者創新點:提出了一種片外 sram地址空間轉換模式,將一維的存儲空間抽象為二維存儲,可以使視頻象素點與存儲空間一一對應;提出了一種 24bit/16bit轉換模塊設計方式。

評論