基于FPGA高速實(shí)時(shí)數(shù)據(jù)傳輸系統(tǒng)設(shè)計(jì)方案

由 DVI[1]解碼芯片輸入給 fpga的像素時(shí)鐘信號 Pclk、數(shù)據(jù)使能信號 DE以及場同步信號 Vsy表示 24bit并行像素數(shù)據(jù)的同步信息。例如: 1024×512顯示分辨率的圖像,則在每兩個(gè)場同步信號 Vsy脈沖之間有 512個(gè)“DE=1”的數(shù)據(jù)有效信號,而在每個(gè)“ DE=1”的數(shù)據(jù)有效信號中有 1024個(gè) Pclk像素時(shí)鐘信號,如此可將輸送的像素?cái)?shù)據(jù)同步。

寫緩沖區(qū)控制器直接接收輸入的 DVI數(shù)據(jù)同步信號,在每個(gè) Vsy脈沖來時(shí)將寫緩沖區(qū)寫入地址清零,然后在“DE=1”時(shí)寫緩沖區(qū)控制器內(nèi)的地址計(jì)數(shù)器計(jì)數(shù)有效,在每個(gè) Pclk上升沿進(jìn)行計(jì)數(shù)加 1操作,這樣在每個(gè) DE有效時(shí)會產(chǎn)生一行的像素?cái)?shù)據(jù)地址,再到下一個(gè)DE有效時(shí)地址計(jì)數(shù)器又會重新計(jì)數(shù),如此循環(huán),而寫緩沖區(qū)會按照對應(yīng)的地址將輸入的 24bit并行像素?cái)?shù)據(jù)同步寫入緩沖區(qū)內(nèi)。寫緩沖區(qū)控制器會在地址計(jì)數(shù)器計(jì)數(shù)到半行數(shù)據(jù)地址的時(shí)候,向內(nèi)存控制器發(fā)送寫緩沖區(qū)讀請求信號( wcache_rreq)和相應(yīng)緩沖區(qū)地址,要求內(nèi)存控制器對已寫入的半行像素?cái)?shù)據(jù)以 48bit并行數(shù)據(jù)格式進(jìn)行讀取,由于內(nèi)存控制器的等效操作時(shí)鐘遠(yuǎn)遠(yuǎn)高于寫緩沖區(qū)的寫入時(shí)鐘,因此內(nèi)存控制器會迅速的將已寫入的半行數(shù)據(jù)讀出并停止讀數(shù),等待下一個(gè) wcache_rreq的到來,如此便形成了對寫緩沖區(qū)的乒乓操作,保證了輸入像素?cái)?shù)據(jù)的正確和連續(xù)接收,避免產(chǎn)生像素?cái)?shù)據(jù)漏接和不同步的現(xiàn)象。讀緩沖區(qū)控制器的設(shè)計(jì)思路同上,不再贅述。

3.2 內(nèi)存控制器的設(shè)計(jì) [5] [6]

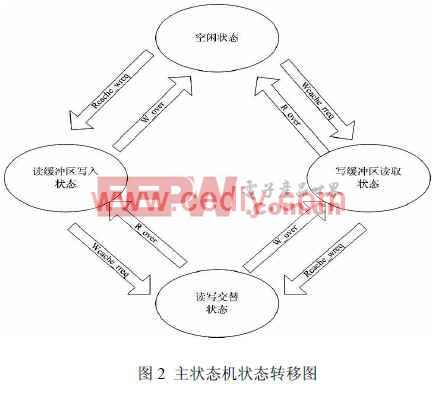

內(nèi)存控制器里包含主狀態(tài)機(jī)和內(nèi)存控制模塊,如圖二所示,主狀態(tài)機(jī)負(fù)責(zé)對兩個(gè)緩沖區(qū)和片外靜態(tài)存儲器的讀寫狀態(tài)控制,共有四個(gè)狀態(tài)――空閑狀態(tài)、寫緩沖區(qū)讀取狀態(tài)、讀緩沖區(qū)寫入狀態(tài)和讀寫交替狀態(tài),用于控制狀態(tài)機(jī)狀態(tài)轉(zhuǎn)移的信號包括:寫緩沖區(qū)讀請求信號(wcache_rreq)、寫緩沖區(qū)讀取完成信號( r_over)、讀緩沖區(qū)寫請求信號( rcache_wreq)以及讀緩沖區(qū)寫入完成信號 (w_req)。狀態(tài)機(jī)在沒有任何操作請求下處于空閑狀態(tài),而當(dāng)其接收到“wcache_rreq”信號時(shí),狀態(tài)就會隨之變?yōu)閷懢彌_區(qū)讀取狀態(tài)并進(jìn)行相應(yīng)操作,而當(dāng)讀取操作完成后會有“ r_over”信號傳入狀態(tài)機(jī),狀態(tài)機(jī)又會轉(zhuǎn)入空閑狀態(tài)等待下一信號進(jìn)入,而當(dāng)狀態(tài)機(jī)處于寫緩沖區(qū)讀取狀態(tài)時(shí)接收到了“ rcache_wreq”信號,則狀態(tài)機(jī)轉(zhuǎn)入讀寫交替狀態(tài),此時(shí)會對寫緩沖區(qū)和讀緩沖區(qū)進(jìn)行交替操作,一旦有一個(gè)緩沖區(qū)操作完成時(shí)會輸入相應(yīng)的操作完成信號,此時(shí)狀態(tài)機(jī)即轉(zhuǎn)入對另一緩沖區(qū)的單獨(dú)操作直至操作完成再次進(jìn)入空閑狀態(tài)。整個(gè)狀態(tài)轉(zhuǎn)移過程保證了對讀寫緩沖區(qū)操作請求的及時(shí)響應(yīng),杜絕了由于狀態(tài)沖突導(dǎo)致的漏操作現(xiàn)象。

本文引用地址:http://www.104case.com/article/169485.htm

系統(tǒng)選用的片外靜態(tài)存儲器的地址總線為 19位,數(shù)據(jù)總線為 16位,經(jīng)公式( 1)計(jì)算可知采用三片內(nèi)存的總?cè)萘空每梢源鎯蓤?1024×512顯示分辨率的圖像,這樣可以對存儲器進(jìn)行乒乓操作,在存儲器內(nèi)寫入一場數(shù)據(jù),讀取另一場數(shù)據(jù),兩者交替獨(dú)立進(jìn)行。 (1)

(1)

內(nèi)存控制模塊負(fù)責(zé)對片外存儲器進(jìn)行控制,其控制信號是兩個(gè)低電平有效信號[3]:nWE和 nCS。nCS為片選信號,當(dāng)為高電平時(shí)存儲器處于非工作狀態(tài),此時(shí)不能對存儲器進(jìn)行任何操作,低電平時(shí)為正常工作狀態(tài),可以進(jìn)行讀寫操作;nWE為存儲器寫入信號,當(dāng)置為低電平時(shí)可以對存儲器執(zhí)行寫入操作,置為高電平時(shí)則可以對存儲器執(zhí)行讀取操作。內(nèi)存控制模塊按照主狀態(tài)機(jī)的當(dāng)前狀態(tài)來設(shè)定兩個(gè)控制信號的高低電平對片外存儲器進(jìn)行控制。圖三為在 QuartusII硬件開發(fā)平臺上通過邏輯分析儀實(shí)際采樣出來的片外靜態(tài)存儲器工作時(shí)序波形圖[6],以中圖為例,存儲器由寫入狀態(tài)轉(zhuǎn)為讀取狀態(tài),存儲器的地址總線信號和數(shù)據(jù)總線信號的變化就可看出存儲器狀態(tài)的變化,在寫入狀態(tài)時(shí)地址總線按時(shí)鐘周期發(fā)生變化,同時(shí)會有 48bit并行數(shù)據(jù)寫入相應(yīng)內(nèi)存地址中,而在存儲器進(jìn)入讀取狀態(tài)后,地址總線則變?yōu)樽x取地址,存儲器則會在延遲地址總線一個(gè)時(shí)鐘周期后將 48bit數(shù)據(jù)經(jīng)由數(shù)據(jù)總線讀出。

評論