易修改無需處理器干預的LED燈序電路設計

到現在為止,Verilog符號已經建立,放置到了高層原理設計里,并且連接到了設備的I/ O和時鐘。現在可以生成Verilog代碼來履行某些功能,在這個案例中可使發光二極管閃爍。為了管理序列的邏輯能力,可以在設計里引入一個簡單的數據路徑。

這個數據路徑包含一個8位ALU,其具備精簡指令集,兩個數據寄存器、兩個累積器、位移和比較邏輯、一個4 deep的 8位FIFO。為了保持設計簡單,只用到了兩個ALU,用來將累加器設置為0,每次開啟或關閉序列執行的時候累加器就遞增。對于較復雜的定序設計,開發人員可以聯合多個ALU形成一個16位或24位處理器。這樣的處理器類似于bit-slice處理器,其在70年代和80年代早期比較流行,它可以為次序的子系統提供足夠的處理能力,。

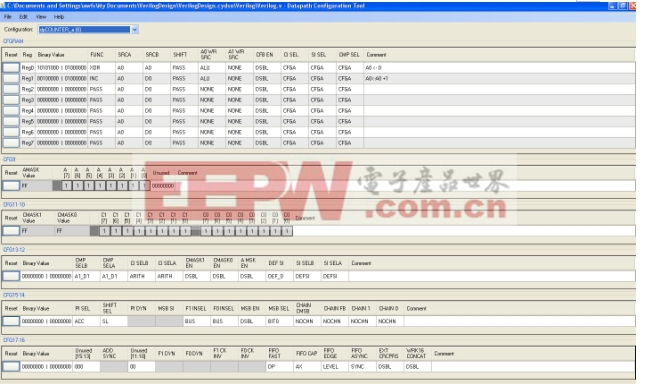

數據路徑配置工具示圖如下。請注意CFGRAM(配置RAM)的前二行注釋:“A0 - 0”,這是給累加器0清零,“A0 - A0+1”,實現在A0累加值。

圖3:數據路徑配置工具。

片上系統(SOC)技術以可編程的方式重新利用了bit-slice技術,用來把處理任務智能地分配到其他可編程硬件,從而減少主CPU的負荷。使用這種方法,可以研制出一種標準狀態機。不同的是,通常算法功能要消耗大量的邏輯門。而在新的方式中這已無需再關注,因為這些功能在標準標準ALU即可實現,它包含由基于PLD的狀態機控制的數據路徑與/或邏輯。

這個設計獨立運行于主CPU。主應用程序可以通過API(可以修改執行參數)控制燈序電路,燈序電路初始化之后,就不再需要CPU。此外,這種實現方式同使用CPU方式相比,本身即可提高效率、可以使用更少的晶體管,從而更好的降低整體系統功耗,給其他特性預留出更多資源。

本文討論了LED燈序電路設計,同樣的設計方法也可用到類似設計,可以通過功能強大的SOC集成結構來執行各種各樣的需要頻繁處理的任務,降低主CPU負荷。現在,工程師不斷面臨很多壓力:提高性能、降低功耗、減少成本…擁有一種像這樣的系統設計工具可以幫助工程師不斷地創造奇跡,達到公眾對他們的期望。

評論