采用AD9913的低相噪頻率合成器設計

根據相位噪聲最優原則,環路濾波器的轉折頻率ωn應取在式(2)、(3)的交點,其閉環特性為:在環路帶寬內,系統輸出的相位噪聲主要取決于參考信號和數字鑒相器基底噪聲,在環路帶寬外,相位噪聲則主要由VCO決定。

本文引用地址:http://www.104case.com/article/164390.htmC波段混頻鎖相合成器設計

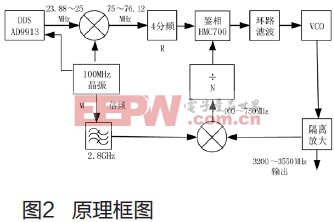

原理框圖

混頻鎖相合成器由DDS電路、混頻電路、壓控振蕩器、鑒相器、環路濾波器、程序分頻器等基本電路構成。具體原理框圖見圖2。

主鎖相環中,3200~3550MHz的輸出信號通過取樣本振下變頻至400~750MHz,分頻后與參考信號鑒相。取樣本振(2.8GHz)由100MHz高穩晶振經倍頻濾波后產生。

本方案中,環路濾波器按500kHz帶寬設計環路參數,因此在近載頻處,對相位噪聲有直接影響的因素是參考信號、倍頻噪聲和鑒相/分頻器本底噪聲,在遠載頻處,相位噪聲則主要受壓控振蕩器的開環特性決定。

AD9913介紹

AD9913是美國ANALOG DEVICES公司生產的新型低功耗直接數字頻率合成器(DDS),它采用先進的DDS技術,結合內部高速高性能的D/A轉換器和比較器,可編程參考時鐘倍乘器形成可編程、可靈活使用的頻率合成功能。AD9913產生高穩定、頻率相幅可編程的正弦波,可作為信號源廣泛應用于通信工程、雷達儀器儀表、高速計算機及導航系統中。

AD9913具有以下重要特性:100MHz模擬輸出和0.058Hz或更高的頻率分辨率;相位噪聲≤-135dBc的每Hz@1kHz偏移(DAC輸出);出色的動態性能:≥80dB的SFDR@100MHz(±100kHz偏移);自動線性掃頻能力;極低功耗(50mw,1.8V電源);可選的PLL REF_CLK倍頻,最高工作時鐘可達250MHz。

AD9913內部集成了DDS模塊、10位DAC、REF_CLK輸入電路、時序和邏輯控制電路以及對外I/O接口模塊等,內部功能方框圖見圖3。

濾波器相關文章:濾波器原理

濾波器相關文章:濾波器原理

分頻器相關文章:分頻器原理 鑒相器相關文章:鑒相器原理 鎖相環相關文章:鎖相環原理

評論