基于有限狀態機的飛行器自毀系統時序控制設計

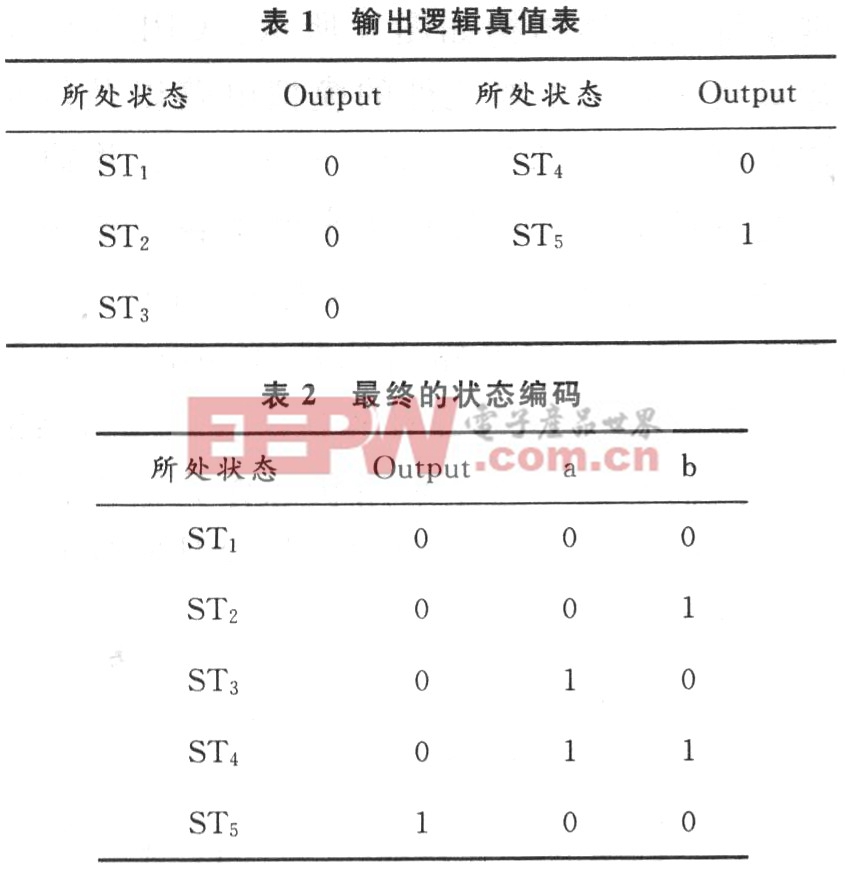

采用VHDL語言描述這種改進的Moore型有限狀態機之前,首先要對Moore型有限狀態機的狀態進行編碼操作。如表1所示,由于有限狀態機的輸出只有Output,為了在綜合時更好地識別這5個不同的狀態,需要添加狀態位。在表2中添加兩個冗余的狀態位a,b來區分STl,ST2,ST3,ST4。本文引用地址:http://www.104case.com/article/163781.htm

3.3 VHDL編程注意事項

本設計采用單進程描述方式,也可以采用兩進程描述。用兩進程時最好把轉移條件判斷邏輯和輸出邏輯分開,這樣有利于綜合器優化代碼,利于用戶添加合適的時序約束,利于布局布線。狀態機要有默認狀態,這是從狀態機的安全性方面考慮的。在狀態機的設計中,一般要包含一個初始狀態,當芯片上電復位時,狀態機能夠進入到初始狀態。這需要在狀態機設計中加入復位信號。

4 電路仿真

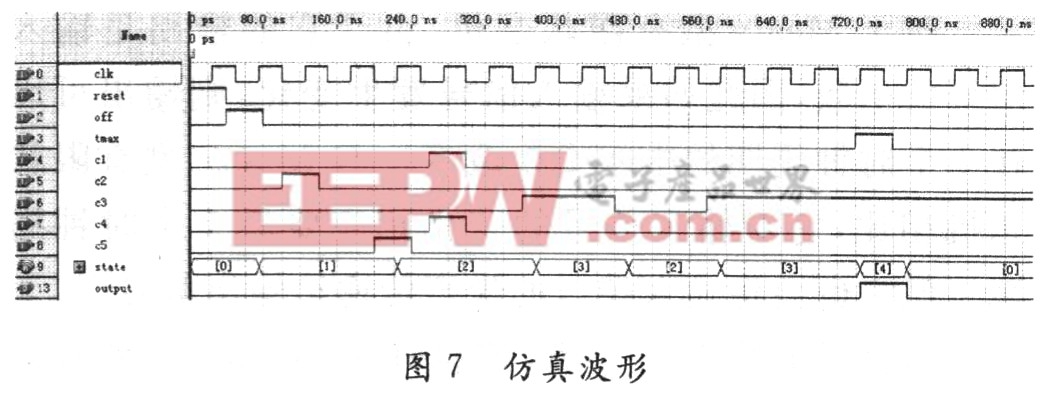

在QuartusⅡ環境下,將VHDL文本程序保存為工程,工程文件經編譯后即可進行電路仿真。仿真波形如圖7所示,從波形結果可以看出,復位信號(reset)有效,使狀態機恢復到初始狀態,飛行器起飛(off)有效開始,時序控制系統經歷了飛行過程中5個不同的狀態,如圖7中state變量所示。并最終輸出自毀指令(Output),VHDL程序設計符合要求。整個時序控制可靠,消除了毛刺現象。在QuartusⅡ環境下,只需要1根下載編程電纜,通過PC機的并行口連接到目標板的JTAG口,將下載信息下載到目標器件中。

5 結 語

仿真及實驗結果證明,采用上述的有限狀態機思想進行飛行器自毀系統時序控制設計,不但可以減小占用CPLD資源,降低成本,方便測試,并且可以有很好的系統性能。基于有限狀態機的飛行器自毀系統定時精度達到納秒級,可以有效可靠地控制自毀信號輸出,有效消除毛刺現象,提高了飛行器自毀系統的穩定性、可靠性。

評論