基于有限狀態機的飛行器自毀系統時序控制設計

摘 要:飛行器自毀系統是飛行器的重要組成部分,它的可靠性和穩定性是飛行器可靠工作的基礎。分析飛行器自毀系統工作原理,采用復雜可編程邏輯器件(CPLD)實現了飛行器自毀系統設計,結合CPLD的特點,提出一種基于改進型有限狀態機的飛行器自毀系統時序控制的設計方法,并在CPLD中予以實現。仿真及實驗表明,基于有限狀態機的飛行器自毀系統定時精度達到納秒級,可以有效地控制自毀信號輸出并消除毛刺現象,很好地滿足系統性能要求。該方法具有結構簡單緊湊、成本低、可靠性高、精度高等優點。

關鍵詞:飛行器;自毀系統;有限狀態機;時序控制

O 引 言

飛行器自毀系統是飛行器的重要組成部分,它具有非常重要的軍事及民用價值。飛行器自毀系統主要是實現飛行器在非正常飛行狀態時的可靠自毀。飛行器按正常狀態飛行,如果出現異常可以通過外部的飛行狀態參數傳感器及自毀電路控制自身自毀。隨著飛行器研制技術的不斷發展,對飛行器自毀系統小型化、模塊化、通用化的要求越來越迫切,CPLD的出現可以滿足這一要求。由于CPLD硬件電路的特點,必須研究適合CPLD硬件架構的設計方法,以達到系統在運行速度與資源消耗上的平衡。有限狀態機及其技術是實用數字系統設計中實現高效率高可靠邏輯控制的重要途徑,有限狀態機是一種簡單、結構清晰、設計靈活的方法,它易于建立、理解和維護,特別應用在具有大量狀態轉移和復雜時序控制的系統中,更顯其優勢。這里針對自毀系統的特點,提出一種符合CPLD結構、基于有限狀態機的設計方法。

l 自毀系統硬件設計

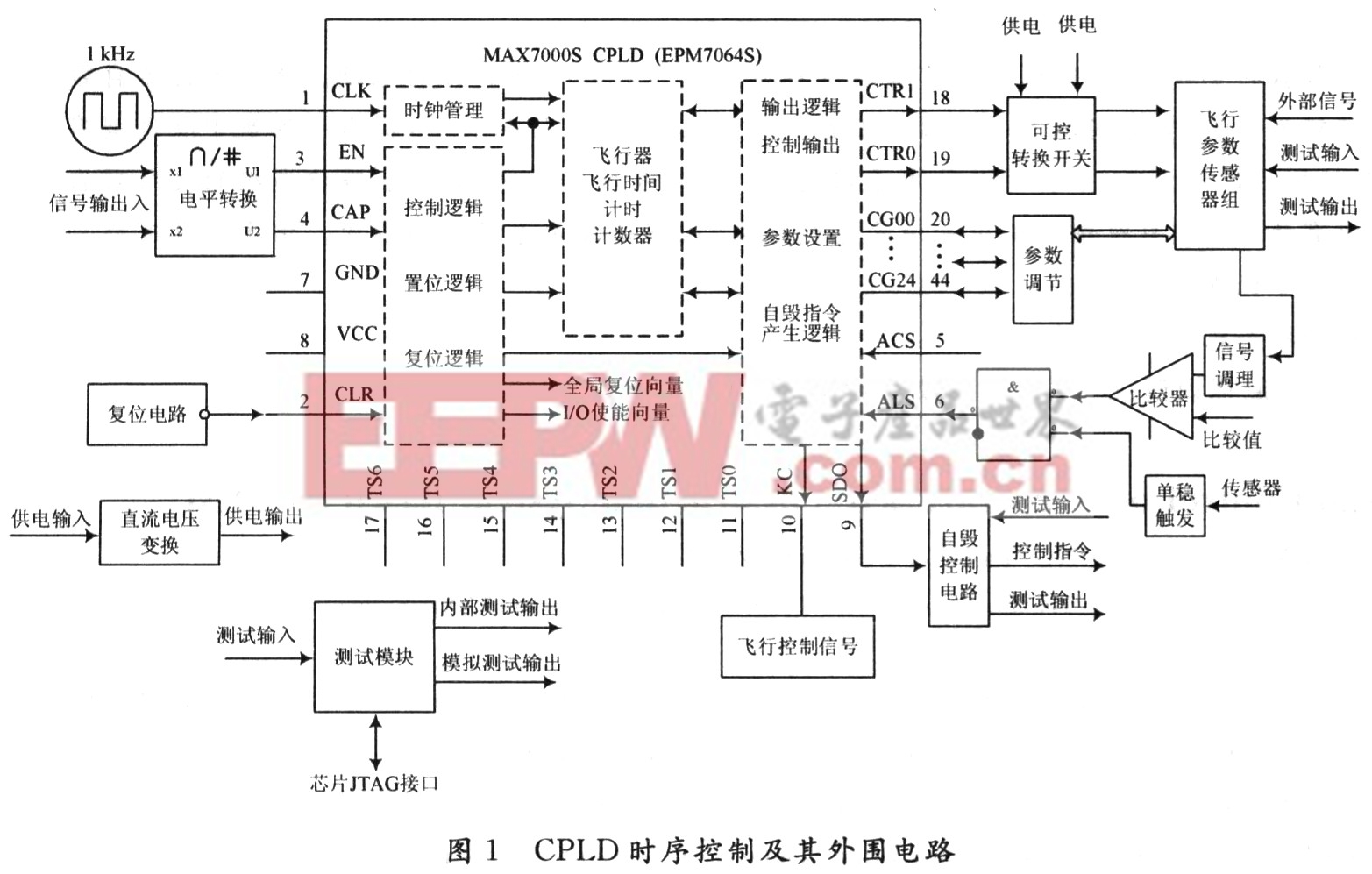

硬件設計采用以高性能CPLD芯片為核心的數字電路和高性能運算放大器及飛行參數傳感器組為主要元件的模擬電路相結合的方案。系統主要由系統時鐘、CPLD控制芯片、飛行參數傳感器組、傳感器組輸出判斷與產生電路、自毀控制邏輯、測試模塊和電源等模塊組成。該設計使用Altera公司的EPM7064SLC44-10芯片,其內部包含有64個宏單元,1 250個可用的系統門,引腳到引腳的邏輯延遲時間為5.0 ns,計數器工作頻率可達175.4 MHz。

用CPLD實現上述自毀條件的時序控制邏輯的核心電路及其外圍電路如圖1所示。CPLD芯片為整個系統的核心,它用來實現計時以及整個系統的時序控制。直流電壓變換電路用于將輸入的直流電壓轉換成EPM7064S所需的電壓,以及外圍電路所需的工作電壓。系統時鐘電路為計時裝置提供穩定的時鐘信號及后續分頻使用的時鐘基準;電平轉換電路將飛行器上輸入信號進行調理后轉換為芯片可識別的TTL/CMOS電平標準;復位電路在系統上電后給控制芯片提供復位信號。

飛行參數傳感器組電路用來實時監控飛行器的各項指標,當飛行狀態出現異常時則由傳感器組產生相應模擬值到由高性能運算放大器及比較器為主要元件的模擬電路。模擬電路對傳感器的輸入值進行處理后送到CPLD時序控制模塊中。可控開關能通過對CPLD編程實現多路轉換,從而使被監控的飛行參數傳感器改變,進而改變飛行器的自毀條件。通過CPLD進行飛行器內部時序控制,最后輸出的自毀指令輸入到飛行控制信號模塊中,從而改變飛行器的飛行狀態,使之自毀。

評論