支持ONFI同步模式的NAND Flash控制器設計

摘要:先對ONFI標準進行了介紹,然后再設計了一種支持ONFI2.1標準源同步高速模式的NAND Flash控制器,包括狀態機的設計,接口的設計等。對設計中遇到的源同步模式下,信號的對齊問題進行了說明,并提出了一種解決方法。同時設計中還會遇到數據跨時鐘域傳輸的問題,本文也給出了解決辦法。最后仿真和綜合結果表明,本文的設計完全滿足標準要求,具有實際的使用價值。

關鍵詞:非易失閃存技術;ONFI2.1;源同步;兩倍數據率;超大規模集成電路

0 引言

在當今的數字信息時代,人們對大容量數據存儲的需求日趨旺盛。作為非易失性存儲器的NAND Flash,由于其高容量低成本的特點,逐漸在實際產品,比如固態硬盤、智能手機、平板電腦等消費類電子產品中得到應用。

由于其特殊的內部結構,NAND Flash的操作方式與NOR Flash不太一樣,不支持隨機字節訪問,其讀、寫操作均要以頁面(Page)為單位進行,同一頁面在未擦除前不允許進行多次寫操作;而擦除操作必須以塊(Block)為單位進行。因此,需要針對這一特性設計專用的控制器來完成各種操作。

本文根據這一目的,設計了一款NAND Flash控制器。該控制器不僅能夠完成前面提到的基本操作,還能支持ONFI2.1標準中的同步接口模式。使其能夠以200MB/s的速度對NAND Flash設備進行讀寫操作,遠遠快于其他同類NAND Flash控制器。

1 ONFI標準

ONFI(Open NAND Flash Interface,開放式NAND閃存接口)規范是一種Flash閃存接口的標準,它是Intel為統一當初混亂的閃存接口所倡導的標準。因為在此之前,市場上銷售的NAND閃存芯片在引腳定義上都不完全相同。這就使得為一家公司設計的控制器,很有可能無法用在另一家公司的產品上。比如為東芝芯片設計的控制器,就無法用在三星或海力士的產品上,這就給上游的主控設計商以及最終的產品設計人員帶來了很大的困難。

為此,Intel聯合多家NAND Flash廠商制定了ONFI標準,統一NAND Flash芯片的引腳定義,并在此基礎上采用新的技術以實現新的功能。2006年發布了ONFI1.O標準,使得接口的統一邁出了實質性的一步。但是該版本速度較慢,最高速度只有34MB/s,不具有太大的競爭優勢。為了提高速度,ONFI組織在2008年發布了ONFI2.0,將接口速度提升到了133MB/s。在該版本中,主要是通過兩項技術來提高傳輸速度。第一項就是在DRAM領域里常用的DDR(Double Data Rate,兩倍數據率)信號技術。第二項是使用源同步時鐘來精確控制鎖存信號,使其能夠達到更高的工作頻率。2009年,ONFI組織又推出了規格更高的ONFI2.1標準,把最高速度提高到了200MB/s。

2 控制器結構

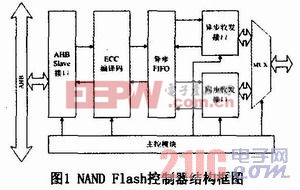

本文設計的NAND Flash控制器是SOC芯片的一部分,作為AHB Slave被掛在總線上,接收來自CPU的讀、寫和擦除等命令。其結構框圖如圖1所示。

其中AHB Slave接口模塊主要是負責處理與AHB總線協議相關的操作;ECC編譯碼模塊主要是負責對存入NAND Flash中的數據進行糾錯編碼和對從NAND Flash中讀出的數據進行糾錯碼譯碼的工作;異步FIFO模塊用來緩存數據,并承擔數據跨時鐘域的工作;主控模塊負責整個控制器的控制;異步收發接口模塊主要負責異步模式下的數據讀寫;同理,同步收發接口模塊主要負責同步模式下的數據讀寫。本文的重點是與ONFI標準相關的接口設計,所以AHB Slave與ECC兩個模塊在此不再介紹,具體請參閱其他相關文獻。

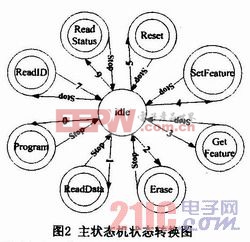

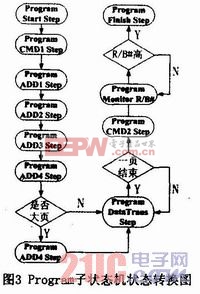

主控模塊是整個控制器的中心控制模塊,由一個主狀態機和多個子狀態機構成。主狀態機有1個空閑狀態和8個工作狀態,分別對應著8種具體的操作。其狀態轉換如圖2所示。而每個工作狀態又對應1個子狀態機,負責每個操作的具體細節。由于篇幅所限,本文只列出Program操作的子狀態機狀態轉換圖,如圖3所示。其他子狀態機的狀態可以根據ONFI標準來確定。

評論