高階QAM調制器的設計與實現

DDS系統輸出信號的頻率為f0=fclk×M/2N,頻率分辨率為△f=fclk/2N,當M=2N-1時,DDS最高的基波合成頻率為f0max=fclk/2。對于本系統,時鐘頻率fclk=155.520 MHz,N取12。仿真結果如圖4所示。

4 系統設計與仿真

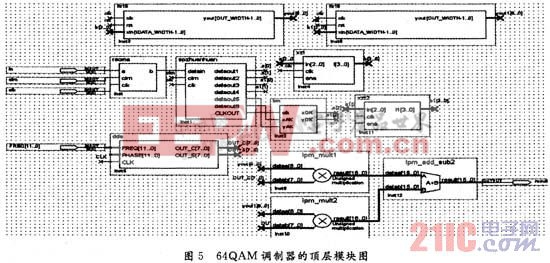

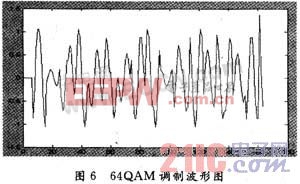

根據以上各模塊單元的設計,構成64QAM調制器的頂層文件如圖5所示。運用QuartusⅡ及Matlab軟件實現64QAM調制器仿真,仿真結果如圖6所示。

仿真可以按不同原則分類:①按所用模型的類型分為物理仿真、計算機仿真、半實物仿真;②按所用計算機的類型(模擬計算機、數字計算機、混合計算機)分為模擬仿真、數字仿真和混合仿真;③按仿真對象中的信號流分為連續系統仿真和離散系統仿真;④按仿真時間與實際時間的比例關系分為實時仿真、超實時仿真和亞實時仿真;⑤按對象的性質分為宇宙飛船仿真、化工系統仿真、經濟系統仿真等。

5 結 語

本文介紹了用FPGA實現全數字高階QAM調制器的思想和方法,采用原理圖和Verilog語言,用可編程芯片StratixⅡ系列中的EP2S30F484C3實現了整個設計,結果表明符合設計要求。為進一步的研究和設計全數字高階QAM系統打下了良好的基礎。

低通濾波器相關文章:低通濾波器原理

矢量控制相關文章:矢量控制原理

評論