基于FPGA的數字磁通門傳感器系統設計和實現

摘要:針對傳統磁通門信號處理電路中模擬元件的缺點,設計一種基于現場可編程門陣列(FPGA)的數字磁通門系統。整個系統采用閉環結構,由激勵產生模塊、信號處理拱塊和負反饋模塊組成。外圍模擬電路用高速D/A、A/D芯片取代,有利于系統溫度穩定性的提到。FPGA內的數字邏輯實現了磁通門信號解算、激勵正弦信號發生、D/A、A/D輸入/輸出串并轉換的功能,首先用硬件描述語言(HDL)設計并仿真,然后下載、配置到FPGA中,調試完成后進行實驗,通過實時處理雙鐵芯磁通門傳感器探頭輸出信號對系統進行測試。實驗結果證實了系統功能的正確性。閉環結構的采用提高了系統信號梯度線性度,與模擬系統相比,基于數字邏輯的設計溫度性能更穩定,更易于小型化,可移植性更強。

關鍵詞:磁通門;現場可編程門陣列;硬件描述語言;信號梯度線性度

0 引言

磁通門傳感器最早于1935年發明并投入應用,用于靜態或者低頻變化的弱磁檢測,擁有其他磁敏元件難以媲美的靈敏度和可靠性,在磁場測量領域一直占據著不可替代的位置。磁通門傳感器適用于地磁或人體磁場的檢測,在航空、航天、地質勘探、醫療衛生等領域有著廣泛的應用。

磁通門傳感器探頭通常采用類似于變壓器的雙鐵芯結構,利用軟磁鐵芯變化磁導率的特性將被測磁場調制成激勵信號的偶次諧波。信號處理系統對探頭輸出加以處理,從中提取與被測磁場大小相關的信號,轉換成直流量并輸出。

傳統的磁通門信號處理電路采用模擬元器件,溫度性能嚴重地受到影響,且很難小型化,可移植性也很差。與之相比,現代數字磁通門系統,溫度性能穩定,體積小,可移植性強。根據應用的具體情況,可選的實現方式多樣,有單片機、可編程數字邏輯,或數字信號處理(DSP)芯片等。

FPGA(Field Programmable Gate Array)是一種高速的可編程邏輯芯片,具有其他設備難以比擬的靈活性,其大部分引腳的功能、內部電路結構完全由用戶根據需要定義。FPGA器件具有很高的實用價值,一方面可以作為專用集成電路的替代品,直接在最終產品中使用,另一方面,也可以在專用集成電路開發流程中,做行為驗證工具。

在本文中,描述了一種基于FPGA的磁通門系統的實現,系統采用閉環結構,對磁通門傳感器探頭輸出的數據進行實時處理,提取出反映被測低頻磁場大小的直流信號。

1 磁通門系統結構和工作原理

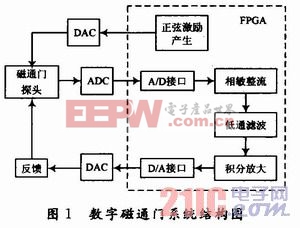

如圖1所示,整個系統的硬件包括磁通門傳感器探頭,DAC,ADC和FPGA。功能上可分為傳感器激勵源、磁通門信號解算、負反饋回路三個模塊。

FPGA內的正弦激勵發生電路和外部DAC一起構成傳感器激勵源模塊。高速ADC和FPGA內的A/D接口、相敏整流、低通濾波電路構成磁通門信號解算模塊。積分放大、D/A接口、高速DAC,以及反饋網絡共同構成了負反饋模塊。

評論