基于FPGA的頻率特性測試儀的設計

3 相頻特性測量模塊

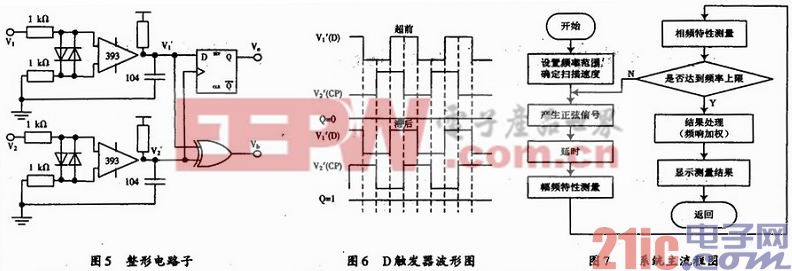

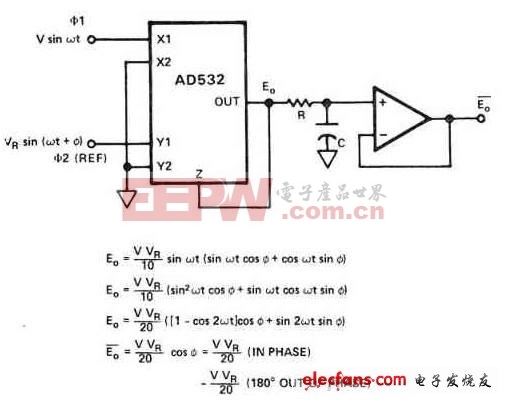

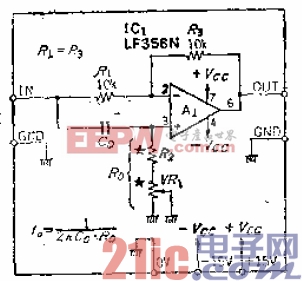

該模塊采用相位一時間轉化法。掃頻信號經過被測網絡只是相位和幅度發生了變化,而頻率保持不變。將被測網絡的輸入輸出信號分別通過LM393整形電路變成方波信號,電圖如圖5所示,將得到的兩路方波信號同時送入FPGA測相電路中進行異或運算,運算后產生脈寬為Tx,周期為T的方波,測相電路只要測出Tx/T,相位差的大小也就確定了。本文引用地址:http://www.104case.com/article/159408.htm

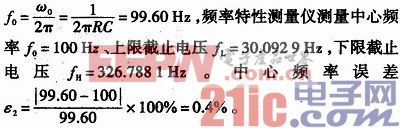

相位的超前與滯后的判斷則通過D觸發器來完成,將整形后的被測網絡的輸入信號V1’加到D觸發器的D端,將整形后被測網絡的輸出信號V2’作為觸發器的CP信號,若V2’超前V1’,則對應V2’上升沿處,V1’為0,則D觸發器輸出為0。反之,V2’滯后V1’,則D觸發器輸出為1。波形如圖6所示。

4 LCD觸摸屏模塊

本系統選用320x240圖形點陣液晶顯示模塊,顯示測量得到的電路網絡頻率特性曲線、漢字、字母、數字、圖形等;在液晶顯示模塊的基礎上再增加觸摸面板。

使用戶更方便地在屏幕上對各參量進行控制,將輸入界面和輸出界面一體化,使人機界面更加優秀。由于液晶顯示控制時序比較復雜,本系統采用FPGA將處理后的數據經過緩存后送入單片機中進行顯示控制。控制過程中在界面底層通過程序繪制頻率特性直角坐標系,在上方圖層繪制一道可以左右移動的屏標。通過按鈕(設置為低電平觸發中斷)控制其移動。將要顯示的參數分布顯示在屏幕上。

5 系統軟件設計

系統軟件設計主要由C語言和VHDL語言編寫完成,前者主要完成顯示控制,后者設計包括監控模塊、測試功能管理模塊、DDS控制模塊、掃頻測試模塊、數據處理模塊等。系統軟件主流程如圖7所示。

6 測試結果

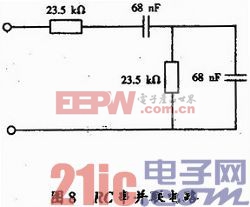

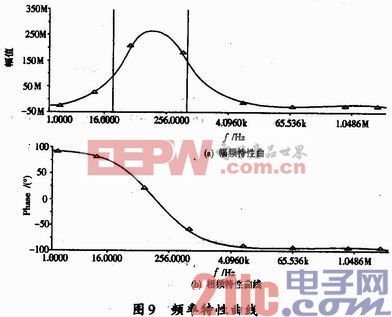

為了驗證該頻率特性測試儀的性能,對圖8中RC串并聯電路進行了測試,顯示的頻率特性曲線如圖9所示。理論計算可得:電路中心頻率

7 結語

本系統在完成軟硬件設計調試以后,對RC串并聯網絡進行了幅頻特性測試。在測試中,系統工作穩定,較好地顯示了測試電路的幅頻、相頻特性曲線,測量精度高,實時性強;本系統已成功運用FPGA設計了一種結構簡單、成本低廉的頻率特性測試儀,為以后設計便攜式頻率特性測試儀提供了參考和依據。

模擬信號相關文章:什么是模擬信號

fpga相關文章:fpga是什么

低通濾波器相關文章:低通濾波器原理

鎖相環相關文章:鎖相環原理 網線測試儀相關文章:網線測試儀原理

評論