FPGA設計經驗談

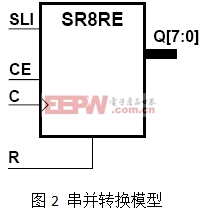

上面這段always實現的是帶同步清零端的串并轉換移位寄存器,位寬為width,下圖為8位電路模型

本文引用地址:http://www.104case.com/article/158978.htm

當你具備了一定的識代碼能力之后,你會發現原來Verilog不是那么的枯燥,只不過是一個個電路模型的拼搭而已。

2)組合邏輯中的if...else...與case

對于多輸入端的組合邏輯來說,如果不需要考慮優先級應該盡量采用case語句來描述,這樣綜合出來的電路并行度要大一些,如果采用if...else...結構,綜合出來的電路都是串行的,增大了信號時延路徑。降低寄存器間組合路徑的延遲是提高系統工作頻率的主要手段,因此在完成相同功能的前提下應該盡量使用并行結構邏輯。

可以看出,并行模式比串行模式少了一級延時路徑,隨著輸入端的增多,串行邏輯將比并行邏輯產生更多的延時路徑。

3)用數學思維來簡化設計邏輯

學習FPGA不僅邏輯思維很重要,好的數學思維也能讓你的設計化繁為簡,所以啊,那些看見高數就頭疼的童鞋需要重視一下這門課哦。舉個簡單的例子,比如有兩個32bit的數據X[31:0]與Y[31:0]相乘。當然,無論Altera還是Xilinx都有現成的乘法器IP核可以調用,這也是最簡單的方法,但是兩個32bit的乘法器將耗費大量的資源。那么有沒有節省資源,又不太復雜的方式來實現呢?我們可以稍做修改:

將X[31:0]拆成兩部分X1[15:0]和X2[15:0],令X1[15:0]=X[31:16],X2[15:0]=X[15:0],則X1左移16位后與X2相加可以得到X;同樣將Y[31:0]拆成兩部分Y1[15:0]和Y2[15:0],令Y1[15:0]=Y[31:16],Y2[15:0]=Y[15:0],則Y1左移16位后與Y2相加可以得到Y;則X與Y的相乘可以轉化為X1和X2分別與Y1和Y2相乘,這樣一個32bit*32bit的乘法運算轉換成了四個16bit*16bit的乘法運算和三個32bit的加法運算。轉換后的占用資源將會減少很多,有興趣的童鞋,不妨綜合一下看看,看看兩者差多少。

4)時鐘與觸發器的關系

“時鐘是時序電路的控制者”這句話太經典了,可以說是FPGA設計的圣言。FPGA的設計主要是以時序電路為主,因為組合邏輯電路再怎么復雜也變不出太多花樣,理解起來也不沒太多困難。但是時序電路就不同了,它的所有動作都是在時鐘一拍一拍的節奏下轉變觸發,可以說時鐘就是整個電路的控制者,控制不好,電路功能就會混亂。打個比方,時鐘就相當于人體的心臟,它每一次的跳動就是觸發一個CLK,向身體的各個器官供血,維持著機體的正常運作,每一個器官體統正常工作少不了組織細胞的構成,那么觸發器就可以比作基本單元組織細胞。時序邏輯電路的時鐘是控制時序邏輯電路狀態轉換的“發動機”,沒有它時序邏輯電路就不能正常工作,因為時序邏輯電路主要是利用觸發器存儲電路的狀態,而觸發器狀態變換需要時鐘的上升或下降沿!由此可見時鐘在時序電路中的核心作用!

逆變器相關文章:逆變器原理

fpga相關文章:fpga是什么

可控硅相關文章:可控硅工作原理

pwm相關文章:pwm是什么

c語言相關文章:c語言教程

逆變器相關文章:逆變器工作原理

比較器相關文章:比較器工作原理

評論