帶RF輸出的全數字調制器設計

軟件定義無線電(SDR)終端促進了物理層功能的可編程實現。很多研究工作已經應用DSP和FPGA實現物理層的基帶功能。

SDR無線電是如此定義的電臺,其天線后面的某段實現了數字化。其后電臺可用柔性及可配置的功能模塊來實現DSP算法。隨著技術的進步,數字化可以在天線后,或非常接近于天線,如此幾乎所有的無線電功能都可以使用高速可編程的DSP引擎通過軟件實現。

目前的無線電結合了模擬和數字構造模塊。RF功能還是適合模擬電路實現,而基帶功能更適合于DSP的實現。數字化前端(DFE)常用來連接RF及基帶處理。DEF通常能夠處理10MH左右的頻率信號,常被稱為數字中頻(IF)。因此,重要的模擬模塊留在了RF和IF之間。

數字RF收發器可擴展軟件定義功能到射頻頻段。所有數字發射機的關鍵優勢是高效的功率放大;數字化合并多通道信號;以及軟件的可編程或可重配置性。

使用全數字發射機,整個發射機可以用DSP或FPGA實現,可以利用CMOS技術增強中的性能。除了與SDR兼容,基于DSP的RF系統可補償RF通道的不平衡性。因此,直接在射頻產生數字信號吸引了很多研究人員和工程師的興趣。

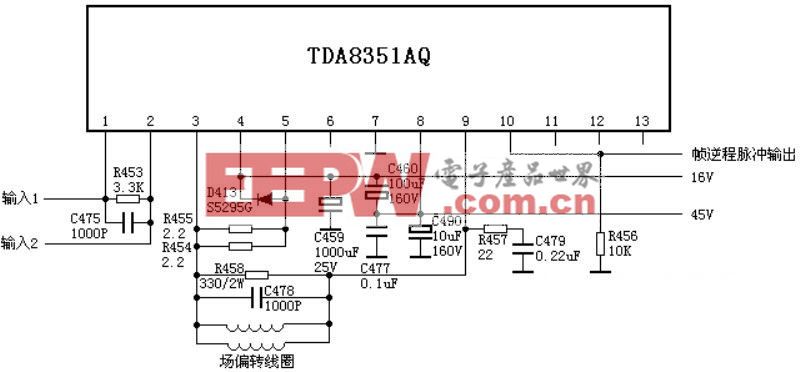

一種比較傳統的方法使用帶通delta-sigma調制在無線電頻率上產生二進制信號。二進制信號可與開關模式功率放大器(PA)一起使用以實現比其他功放技術更高的效率(圖1)。這種體系結構的限制是帶通delta-sigma (BPDS)調制在中心頻率的四倍處運行,達到幾千兆赫。為了適應如此高的頻率操作,定制的IC必須仔細設計,不具備重新編程能力。

|

采用BPDS的數字發射機 |

另外一種方式是用脈寬調制(PWM)數字合成二進制RF信號。PWM是很久以前提出的一種模擬調制,但是最近流行起來,特別是在數字音頻放大應用上。D類音頻PA,由PWM音頻信號驅動,可達到90%以上的效率。Delta-sigma類型調制也可用于數字PWM,但與BPDS方式比較運行在較低頻率。然而,delta-sigma環路傾向于比BPDS更復雜,由于其較低的過采樣率和PWM有關的非線性。

測試配置使用存儲在測試模式發生器中的離線計算的信號源。在本例中,設計了一個實時系統來演示使用數字PWM的RF信號數字發生器的能力。

數字RFPWM 發生器

由數字功放技術推動的數字PWM,數字信號無須依靠數模轉換器(DAC)就可以直接轉換成高功率模擬信號。由于全數字音頻系統越來越受到關注,數字功放已經在數字音頻應用上開始流行。

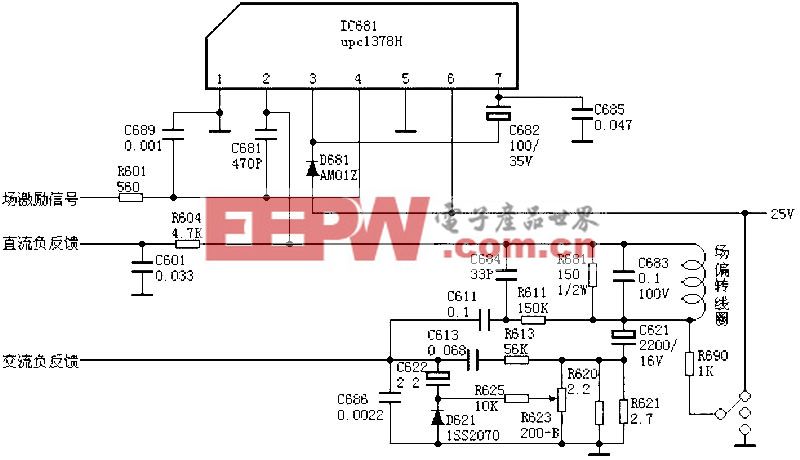

在數字PWM,脈寬以高速時鐘離散化。因此,采樣計數器可根據高速參考時鐘產生數字PWM波形(圖2)。內插器增加PCM輸入的采樣頻率到適合PWM調制的水平。該頻率經常稱為脈沖重復頻率(PRF)。

|

組成數字PWM系統的信號處理模塊 |

正常采樣器是均勻采樣數字信號為基礎計算正常采樣信號值。顯然當采用PWM時,正常采樣信號基帶失真遠小于均勻采樣。

出于實現考慮,量化需確保高速參考時鐘運行在適當地頻率上。例如,PCM的原始輸入是44.1 kHz,16倍內插器將導致705.6 kHz的PRF。若脈寬量化到16位,高速參考時鐘必須達到46-GHz。假如只需要8位量化脈寬的話,高速參考時鐘可至180 MHz。因此,用適當的技術實現將比較容易。噪音成型技術,delta-sigma調制技術,常被用來抑制量化引入的基帶噪聲。

處理密集的模塊、正常采樣器、及噪音成型量化的采樣頻率PRF。這是該工作的主要動機――主要的信號處理算法在較低的PRF而不是RF頻率上執行。

全數字RFPWM

全數字RF PWM稱為正交積分噪音成型(INS),是用于量化及噪音成型模塊的一種算法。其主要目標是抑制基帶脈寬量化處理過程引入的噪聲功率。它不同于其它在反饋環中引入非線性項的算法。不考慮INS算法的細節的話,正交INS可看成是2個獨立的PWM調制器,分別用于復信號的同相(I)和正交分量(Q)。

這些脈寬調制使用以前描述過的相同體系結構。這些PWM輸出的是基帶信號,需要進一步和數字本機振蕩器信號混合形成RF帶通信號。假如基帶PWM及數字本機振蕩器信號都是二進制,混合操作只不過是簡單的邏輯XOR操作。

另一種簡化該混頻操作的方法是使數字本振的同相支路取取當0, 1, 0, -1三值,正交支路取-1, 0, 1, 0。這樣,數字混頻器只輸出-Q, I, Q, -I 序列。當I及Q都是二進制PWM信號時,混頻器的輸出也將是二進制的。為了保證本振信號是2種格式中的一種,取樣頻率必須是4倍本振頻率。來自2個數字混頻器的信號組合成需要的RF信號。

對于PWM調制的信號,信號信息在脈沖寬度中承載。因為脈沖寬度定義為上升沿和下降沿之間的持續時間,在基帶PWM后過度區將被保留。然而,在同相和正交本振信號之間存在90度的相位差。因此,需要特別小心的是必須確信基帶PWM與他們的本振信號分別是同步的的。因為采樣率設置在4倍的本振頻率,相差等于1/4周期。

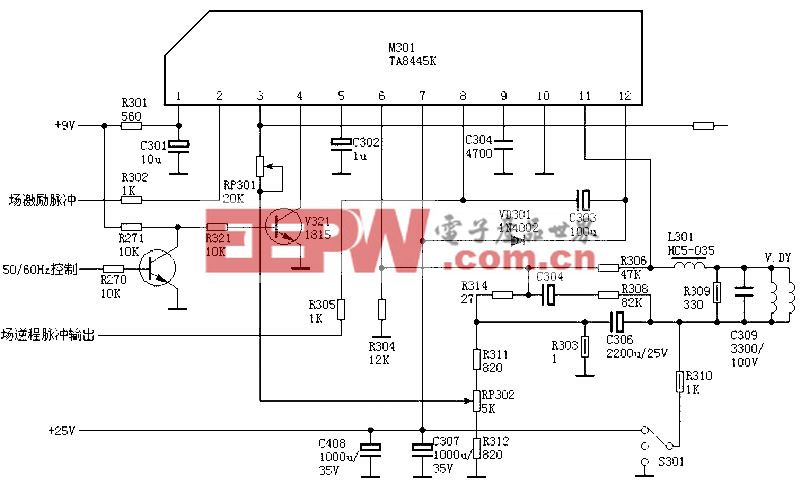

基帶PWM同相、正交波形是分別生成的:內部引入四分之一相差來補充同相和正交本振信號之間的相差。研究基帶PWM和RFPWM的定時波形,本振信號是三值格式,而組合輸出RFPWM信號是二進制。此外,兩個基帶PWM都分別同步到其本振信號的上升沿。

|

顯示了基帶PWM和RFPWM的定時波形 |

此處討論的QAM-PWM調制器使用正交PWM體系結構,由于其高計算能力需求沒有選用INS算法。采用了非遞歸噪聲成型方法。

數字PWM噪音成型

噪音成型廣泛應用于過采樣數據變換器上。噪音成型的目的是產生一個粗量化信號而不是精量化信號,在窄帶上保持SNR性能。在數字PWM系統中,噪音成型在參考時鐘頻率很高時是非常必要的,脈寬精量化,在PRF是705.6 kHz使用16位而不是8位。

傳統數據轉換器的噪音成型濾波器已經研究的很透,大部分方法也可用在數字PWM上。但是在數字PWM上噪音成型的行為不同于傳統的DAC,這是因為PWM引入了非線性。

仿真模型比較了PWM與傳統的DAC(圖4)。數字PWM和傳統的DAC使用相同的噪音成型濾波器及量化器。在該仿真器中噪音傳輸函數(NTF)用H(z) = (1-z-1)N規定,N取值在1到5之間。就帶內噪聲抑制來說該類型噪音成型濾波器不是最佳的,但足以演示PWM與傳統DAC的不同。DAC的模擬部件不包含在仿真器中;僅僅考慮了所有數字噪音成型環路。下面是為仿真器所選的參數:

輸入的單音信號頻率 =11 kHz,基帶帶寬 =20 kHz,采樣頻率 =705.6 kHz,輸入信號電平 =-6 dB,FS量化級別 =64

對于傳統的DAC,量化級別指示出最終的DAC使用的比特位數,而對PWM,則意味著高速時鐘在每一個脈沖周期的取值范圍(表1)。

|

PWM和傳統DAC噪音整形的仿真比較 |

|

表1 |

當使用低階NTF時,也就是,N = 1和N = 2PWM和傳統DAC的信噪比測量幾乎是一樣的。當NTF階數增加時,PWM的信噪比傾向不同于傳統的DAC。注意:當N從2增加到3時PWM 信噪比不象傳統DAC那樣迅速改善;且隨著N進一步由4增加到5 PWM的信噪比開始惡化。

如果NTF高頻增益高量化噪音可能折回到基帶。這可由PWM調制的非線性天性解釋。然而,如果僅要求中等程度基帶信噪比情況下,這個非線性的效果可以忽略不計。在整個仿真模型中,我們概括出為數字PWM系統設計一個非遞歸NTF濾波器的準則。該準則包括當濾波器輸入是白噪聲時,最小化基帶功率與總功率的比率。濾波器參數將確保最小相位,歸一化需求,其第一個系數將是1。濾波器高頻增益將受限制。

然后這些準則可用下列數學公式來闡述,假設一個N抽頭FIR濾波器系數為h,這里h = (h0, h1, …, hN-1)T,基帶功率可以計算出來:

|

這里R是矩陣,

|

可以使用Parseval理論計算總功率:

|

因此優化NTF應設法最小化,

|

|

|

硬件原型及測量

如前所述,數字PWM的所有的信號處理算法運行在PRF頻率。唯一必需的高速電路是最終的PWM波形發生器。因此,在現存FPGA器件上構造全數字QAM-PWM調節器是可行的。

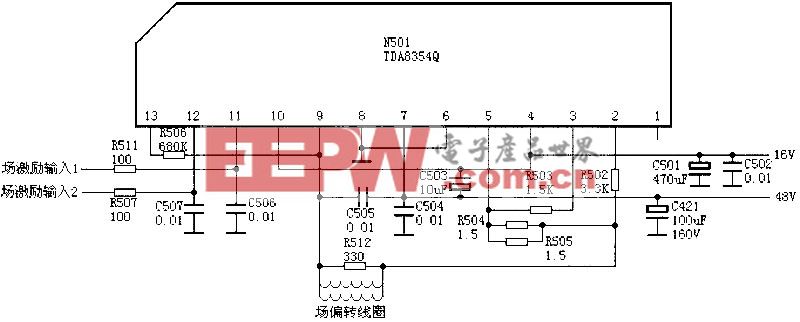

在數字QAM-PWM調制器的體系結構中,正交通道由幾乎相同的體系結構模塊組成(圖5)。QAM調制器由符號速率5.057 MHz的QAM符號發生器、將采樣比率提高到符號速率16倍的插補濾波器,以及一個將采樣率轉換到100 MHz PRF的轉換器組成。

|

全數字RF PWM原型的體系結構圖 |

數字PWM由一個正常采樣器,一個噪音整形量化模塊,和一個PWM波形發生器組成。正常采樣算法僅由前饋數據通路構成;因此相當容易流水線化。噪音整形量化模塊有反饋路徑;因此盡管PRF僅為100 MHz是相當難以實現的。

FIR NTF濾波器使用變化的結構、重新定時技術及反轉部分系數的符號比特(CSD)實現。本振信號與所有可能的基帶PWM信號混頻是預先計算并存儲在ROM 中的。該ROM通過量化輸出,即脈沖量化寬度來訪問。來自同步和正交通道選定的RF PWM波形將在高速串行器產生1位RF信號之前組合。

選做原型的FPGA器件是Xilinx的Virtex2pro,型號XC2VPX20-FF896,速率等級為7。該部件有片上多吉比特收發器,用作高速并到串轉換器以產生3.2 GHz二進制信號(表2)。

|

表2 |

邏輯元素分配的結果是從Synplcity綜合結果抽取的。最后的安置及布線工具報告完整QAM-PWM設計利用了18個乘法器(20%),4個RAM16 (4%),3911個基本單元(39%)。注意:括號中的數字有關于總資源的利用率。

當帶通噪音電平低于信號大約45 dB時,更加進取性的噪音整形技術可實現更好的帶通噪音性能。然而在這種情況下計算需求可能不利于可實現性;使用現存的FPGA將是困難的。EVM測量值小于1%,幾乎與QAM輸出端測量的EVM一樣。

評論