RF ADC為什么有如此多電源軌和電源域?

在采樣速率和可用帶寬方面,當今的射頻模數轉換器(RF ADC)已有長足的發展,其中還納入了大量數字處理功能,電源方面的復雜性也有提高。那么,RF ADC為什么有如此多不同的電源軌和電源域?

本文引用地址:http://www.104case.com/article/202407/460824.htm隨著硅處理技術的改進,晶體管的幾何尺寸不斷減小,意味著每 mm2面積上可以容納更多的晶體管(即特征)。但是,人們仍然希望 ADC 實現與其前一代器件相同(或更好)的性能。 現在,ADC 的設計采取了多層面方法,其中: 1. 采樣速度和模擬帶寬必須得到改善; 2. 性能必須與前一代相同或更好; 3. 納入更多片內數字處理功能來輔助數字接收邏輯。

需要高速度

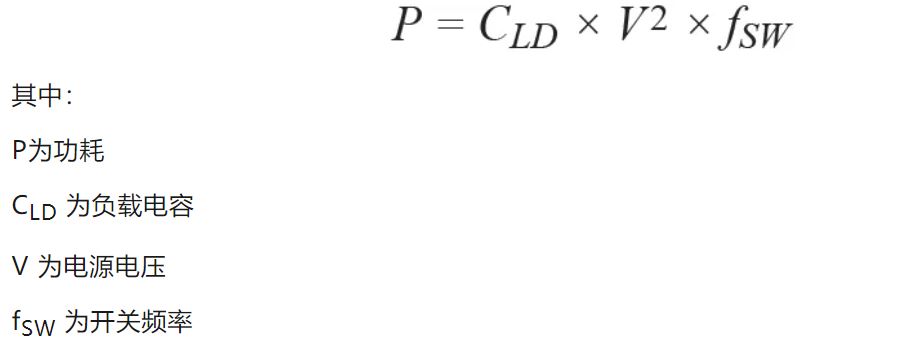

在 CMOS 技術中,提高速度(帶寬)的最普遍方法是讓晶體管幾何尺寸變小。使用更精細的 CMOS 晶體管可降低寄生效應,從而有助于提高晶體管的速度。晶體管速度越快,則帶寬越寬。數字電路的功耗與開關速度有直接關系,與電源電壓則是平方關系,如下式所示:

幾何尺寸越小,電路設計人員能實現的電路速度就越快,而每MHz每個晶體管的功耗與上一代相同。以 AD9680 和 AD9695為例,二者分別采用65 nm和28 nm CMOS技術設計而成。在1.25 GSPS和1.3GSPS時,AD9680和AD9695的功耗分別為3.7 W和1.6 W。這表明,架構大致相同時,采用28 nm工藝制造的電路功耗比采用65 nm工藝制造的相同電路的功耗要低一半。因此,在消耗相同功率的情況下,28 nm工藝電路的運行速度可以是65 nm工藝電路的一倍。AD9208很好地說明了這一點。

裕量最重要

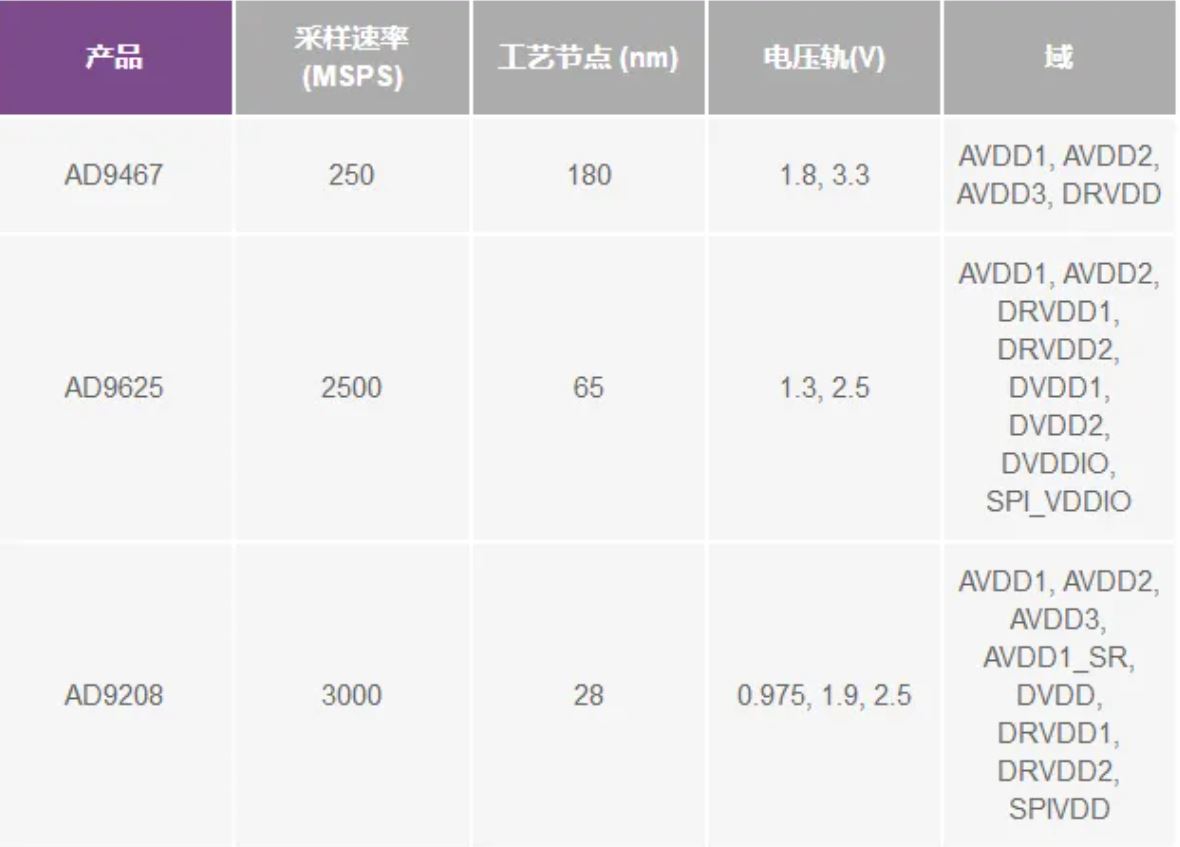

表1:產品比較

隔離是關鍵

為了改善隔離,設計者必須考慮各種耦合機制,最明顯的機制是通過共享電源域。如果電源域盡可能遠離電路,那么共享同一電壓軌(AD9208為0.975 V)的數字電路和模擬電路發生震顫的可能性將非常小。在硅片中,電源已被分開,接地也是如此。封裝設計繼續貫徹了這種隔離電源域處理。由此所得的同一封裝內不同電源域和地的劃分,如表2所示,其以AD9208為例。

表2:AD9208電源域和接地域

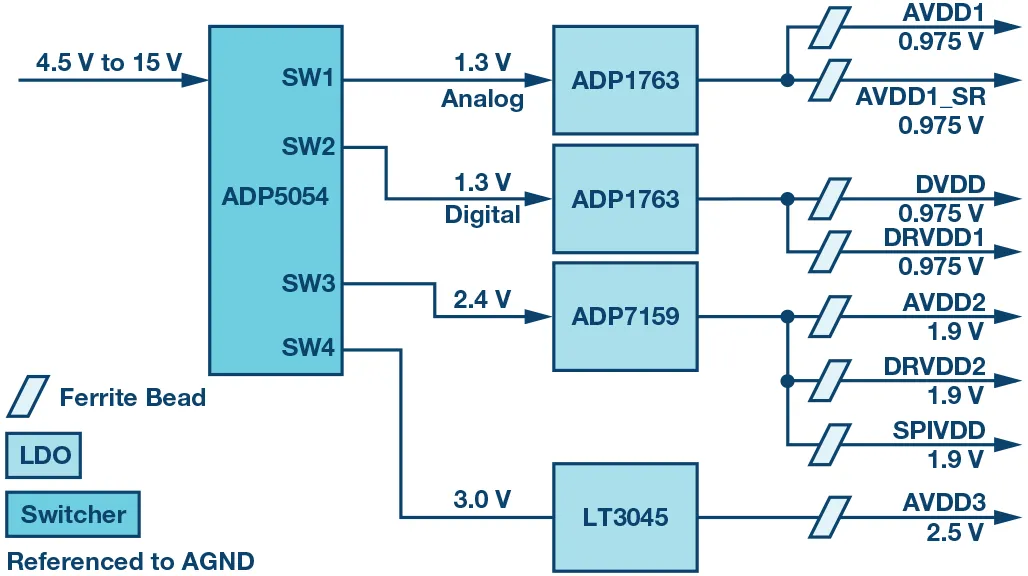

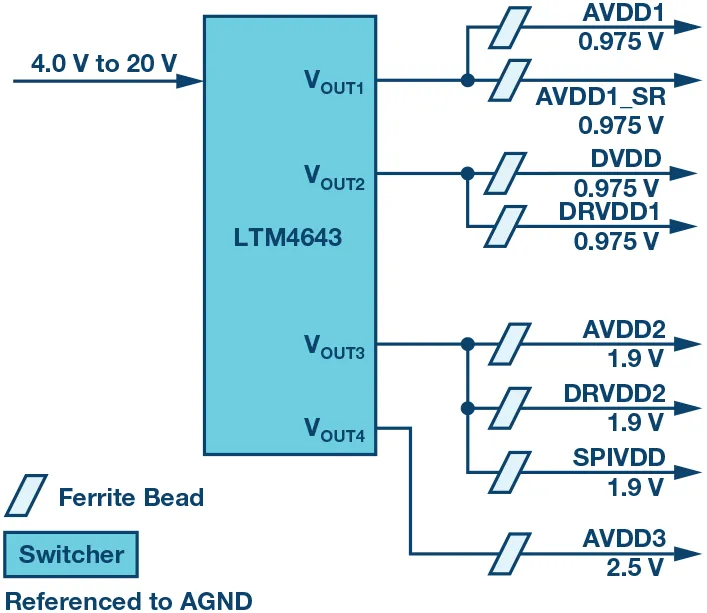

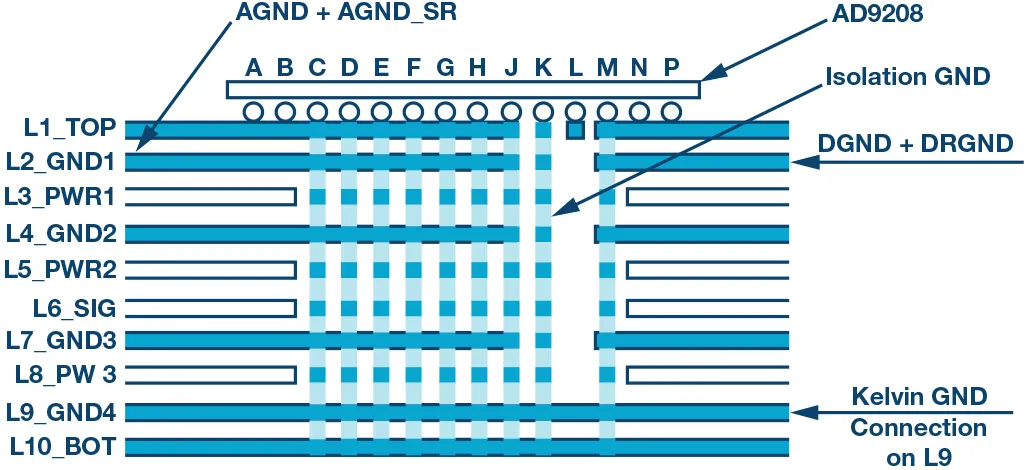

這可能會讓系統設計人員驚慌失措。乍一看,數據手冊給人的印象是這些域需要分開處理以優化系統性能。情況并不像看起來那么可怕,數據手冊的目的僅僅是喚起人們對各種敏感域的關注,讓系統設計人員可以關注PDN(電源輸送網絡)設計,對其進行適當的劃分。共享相同供電軌的大多數電源域和接地域可以合并,因此PDN可以簡化。這導致BOM(物料清單)和布局得以簡化。根據設計約束,圖2和圖3顯示了AD9208的兩種PDN設計方法。

圖3. AD9208 PDN,DC-DC轉換器為所有域供電 圖4. AD9208下方的AD9208-3000 EBZ PCB橫截面

文章來源:亞德諾半導體

評論