基于FIFO的DDC與DSP高速數據傳輸實現

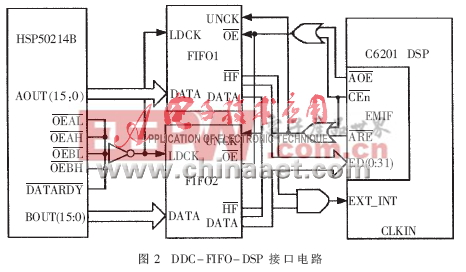

2.2 FIFO與DSP EMIF接口

TMS320C6201的外部存儲器接口(EMIF)是32位接口,HSP50214B的AOUT和BOUT兩路16位分別經兩FIFO的低16位與EMIF的 32位接口連接,DSP同時讀取AOUT和BOUT兩路數據存放于內部存儲器,數據在存儲器中奇偶分離,可以采用32位或16位的訪問方式存取數據,這樣充分利用DSP的硬件資源,保證了數據的高速傳輸。由于TMS320C6201只有一個外部總線接口,FIFO與DSP通過EMIF相連接,所以必須注意數據采集與連接到外部總線上的其他外部設備或存儲器對使用總線的沖突,要保證沒有其他外圍設備長時間占用外部總線,否則發生總線使用沖突時將導致采集數據丟失。

對于讀FIFO的讀操作,這里用到EMIF異步存儲器控制信號:輸出使能(/AOE)和讀使能(/ARE)以及外部空間選擇信號(/CE0)。DDC、FIFO、DSP間的接口電路如圖2所示。從圖2中邏輯關系可看出,當/AOE與/CEn都有效時,OE有效,片選使能兩個FIFO。當/CEn和/ARE同時低電平有效時,UNCK無效,待讀出的數據在此時進行初始化,隨后ARE會跳變為正電平,使UNCK產生上升沿,FIFO中數據被讀出。圖2中兩個FIFO的半滿信號HF經過一個“與”門連接至DSP外部中斷引腳EXT-INT5。當兩個FIFO皆達到半滿時“與”門輸出由低變高,上升沿觸發DSP外部中斷EXT-INT5,DSP啟動DMA(直接存儲器存取)以突發的方式讀取FIFO數據。FIFO1中數據作為低16位,FIFO2中數據作為高16位,合并為32位數據讀入DSP內部存儲空間。

本文引用地址:http://www.104case.com/article/158169.htm

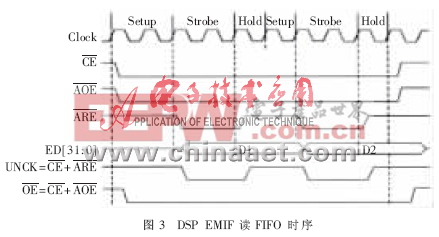

本文引用地址:http://www.104case.com/article/158169.htm3 接口時序

設計中,FIFO采用半滿信號。若FIFO使用滿(/FULL)狀態信號,則滿(/FULL)狀態位有效時,觸發DMA開始數據傳輸;如在滿信號和DMA傳輸之間仍有數據出現在數據線上,則因為此時LDCK對FIFO無效,待DMA開始數據傳輸時才允許數據寫入,所以可能丟失采集數據。本設計中采用半滿(HF)信號作為標志位,在半滿時,開始DMA傳輸,不中斷數據寫入FIFO。由于ADC數據寫入FIFO速度小于EMIF讀出速度,所以后續數據不會覆蓋原來的有效數據,采樣數據不會丟失。

EMIF讀FIFO邏輯關系如下:UNCK=/CE+/ARE,LDCK=/CE+/AWE,OE=/CE+/AOE,讀FIFO時序如圖3所示。

本設計利用雙FIFO結構實現DDC與DSP間的32位數據緩沖,保證了數據的高速有效傳輸。FIFO與DSP采用32位的接口方式,DSP EMIF讀取FIFO采用DMA的數據傳輸方式,充分利用了DSP的硬件資源以提高系統實時處理能力,能夠滿足軟件無線電的中頻數字信號處理要求。

評論