DS/FH混合擴頻接收機解擴及同步技術的FPGA實現

相關累加器完成本地偽碼與接收信號的相關累加運算,運算得到的結果送入DSP完成偽碼的捕獲和跟蹤。取偽碼長度為256位,采用半碼片滑動,則一個碼周期完成512次累加運算。如采用串行滑動相關捕獲方式,則遍歷所有的碼相位所需要的時間為512個碼周期,即捕獲所需要的最長時間為512個PN碼周期。由于可編程邏輯器件的發展,使得有足夠的硬件資源來完成并行運算。此處采用串/并混合的捕獲方式[6][7],采用8路相關累加器,每一路分為超前、當前、滯后3組,每組相差半個碼片的相位,每一路相差64個半碼片的相位。這樣,只需滑動64個半碼片相位就可以遍歷所有的偽碼相位,完成捕獲所需時間縮短為原來的八分之一。數據解調由另外4組相關累加器完成。由于發射端同步偽碼與數據偽碼相位嚴格對齊,所以在接收模塊中,完成同步偽碼捕獲跟蹤后,直接將所獲得的相位信息用于數據解調相關器,即可正確解調數據。

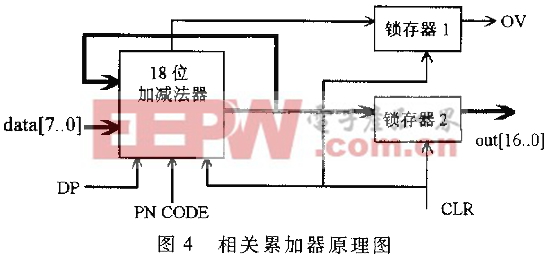

同步偽碼的跟蹤采用超前―滯后延遲鎖相環路(DPLL),每一路相關器包括3組累加器。捕獲跟蹤及數據解調共使用28組相關累加器,每一組相關累加器結構都是完全一樣的,均分為I、Q兩路,分別進行累加運算,完成512次累加運算后由DSP讀取數據。I、Q兩路結構完全相同,其中一路的原理圖如圖4所示。

相關累加器由18位加減法器、鎖存器1和鎖存器2組成,data[7..0]為下變頻后的輸入數據,PN CODE來自碼發生器。作為控制端,低電平完成加運算,高電平完成減運算,DP上升沿進行數據鎖存,下降沿完成一次累加運算。當累加運算完成后,由CLR信號清零并將結果存入鎖存器2,CLR下降沿有效。鎖存器1輸出OV信號作為溢出標志位,鎖存器2輸出累加結果out[16..0]。輸入與輸出端的最高位為符號位。

1.4 本地碼發生器及碼移相電路

本地碼發生器用于產生本地PN碼,從而與接收信號進行相關運算。由于發送端采用編碼擴頻調制方式,接收信號中既有同步PN碼,還有數據PN碼,與接收信號相對應,本地也應該產生相應的PN碼,用于同步及解調數據。

本地PN碼發生器全部采用FPGA實現,并且設置了可編程寄存器和外部接口,DSP通過接口可預置PN碼長度。1024進制計數器電路用于產生ROM的輸入地址,ROM由FPGA內部RAM資源來實現,采用ALTERA公司APEX20K200器件。該器件內部可編程RAM容量為106496位,完全可以滿足設計需求。本地PN碼采用半碼片滑動方式,ROM內部PN碼也以半碼片方式存儲。如碼長為256,采用半碼片存儲方式后,每一組PN碼需存儲512位數據,相應的ROM有9位地址線驅動輸出。驅動時鐘為PN碼時鐘的2倍。在實際設計時,PN碼發生器內存放了8組PN碼,但只用了五組,一組用于同步,另外四組用于解調數據。ROM輸入地址由1024進制計數器產生,實際上只需用512進制計數器即可得到ROM輸入地址。考慮到可擴展性,這里采用了計數容量最大為1024的可變計數器。由DSP通過DSP-FPGA接口改寫寄存器值,可以很方便地調整PN碼的輸出相位。

偽碼移位電路的主要作用是將碼發生器產生的PN碼進行移位操作,從而得到偽碼的不同相位。捕獲和跟蹤過程共使用了8路24組相關累加器,每一路分為超前、當前、滯后3組,這3組累加器輸入端PN碼相差半個碼片的相位,8路相關累加器中每相鄰兩路相差64個半碼片。碼發生器輸出5組PN碼序列(第0組~第4組),分別對應同步偽碼及4組數據偽碼。5組偽碼均經過512級移位寄存器,第0組PN碼作為同步碼,取其0、1、2相位作為第一路的超前、當前、滯后3組相關累加器的輸入;64、65、66相位作為第二路的超前、當前、滯后3組相關累加器的輸入,其余各路依此類推。當完成捕獲后,需要將捕獲所得的同步PN相位切換到數據解調相關累加器中。例如,假設在第二組相關累加器的當前通道捕獲,那么此時解調數據用的相關累加器的PN碼相位就應該與第二組相關累加器當前通道的PN碼相位保持一致。數據偽碼相位切換的實現是由DSP記憶捕獲通道的相位,然后控制多路選擇開關選擇該相位。

評論