基于ADSP-BF533的數字通信信號發生器設計與實現

在通信對抗的研究中,要想模擬出真實數字通信信號場景,數字通信信號發生器是不可或缺的儀器。而市面上的通信信號發生器價格十分昂貴,功能也比較簡單。而且這類通信信號發生器的輸出碼元不可控,信噪比及干信比也不能動態調節,因此無法模擬多種調制類型通信信號的混合環境,用作通信對抗系統的性能測試信號源極為不便。所以開展高精度通信信號及噪聲干擾波形的重構方法研究工作,具有重要的理論意義和實用價值。

1 ADSP-BF533芯片簡介

ADSP-BF533是Blackfin系列的中高性能產品,專門針對多媒體(特別是視頻處理)和通信方面的各種應用。其內部包含2個乘/累加器(MAC),2個40位的ALU,4個視頻ALU和1個40位移位器。BF533內核工作時鐘可高達600 MHz。運算單元處理來自寄存器組的8位、16位或者32位數據。

BF533的每個MAC每周期可完成一個16位乘16位的乘法運算,并可把結果累加到40位的累加器中,同時可提供8位的精度擴展。其ALU單元執行標準的算術和邏輯運算,兩個ALU可處理16或32位的數據,運算單元具有很大的靈活性.因此可以滿足各種應用中信號處理的要求。

ADSP-BF533把存儲器視為一個統一的4GBytes的地址空間。所有的資源,包括內部存儲器、外部存儲器和I/O控制寄存器,都占據公共地址空間中相應的部分,并且相互獨立。此地址空間的各部分存儲器按分級結構排列,以提供高性能價格比。高速、低延遲、小容量的存儲器(如CACHE或SRAM)的位置非常接近處理器,而低速、高延遲、大容量、低成本的存儲器(如SDRAM或Flash)遠離處理器。

BF533內的L1存儲器是內核中性能最高最重要的存儲器;L2存儲器用以提供額外的存儲能力,性能較低:片外存儲系統通過外部總線接口單元(EBIU)進行訪問;異步存儲器單元可以連接4個異步存儲器bank或IO接口,每個bank可支持最大1MBytes物理尋址空問;同步存儲器單元可以由SDRAM進行擴展,可以訪問多達128MBytes的物理存儲空間;存儲器的DMA控制器提供高帶寬的數據傳輸能力,能夠在內部L1/L2存儲器和外部存儲器空間之間完成代碼或數據的塊傳輸。

另外,ADSP-BF533還提供一個可直接與并行A/D和D/A轉換器、符合ITU-656標準的視頻編碼和解碼器以及其它通用外設連接的并行接口(PPI)。PPI包括一個專用時鐘引腳、多達3個幀同步引腳和多達16個數據引腳。PPI的通用模式分為4種主要的工作方式,即:內部產生幀同步中信號的數據接收,外部產生幀同步信號的數據接收,內部產生幀同步信號的數據發送,外部產生幀同步信號的數據發送。每種每個PPI_CLK時鐘周期可傳送高達16 bits的數據,廣泛應用于各種數據采集和數據傳輸的場合。

2系統硬件設計

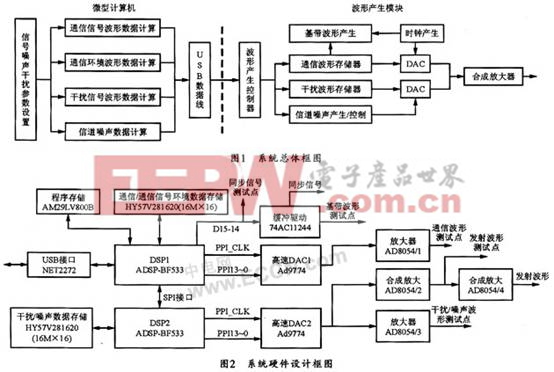

數字通信信號發生器系統分為兩大模塊:微型計算機模塊和波形產生模塊。其中微型計算機為通用計算機或PC,波形發生模塊為設計的信號發生板卡。圖1所示為系統總體框圖。

通用微型計算機首先根據用戶輸入的參數.分別產生各種類型的數字調制信號和高斯窄帶白噪聲及各種類型的干擾信號,然后將數據通過USB接口傳送到信號發生板卡。信號發生板卡再通過波形產生控制器循環取出通信波形存儲器和干擾/噪聲存儲器中的數據,最后通過DAC產生連續的數字通信信號波形。圖2所示為系統硬件設計框圖。

硬件設計中的DSP1為整個系統的核心,可直接和微型計算機通信,并且控制著DSP2的加載和運行。DSP1的加載方式為BMODE 01方式,從外部Flash加載;DSP2為BMODE 10方式,通過SlaveSPI接口加載。

DSP1首先接收微型計算機通過USB接口傳送的波形數據包,并將數據包中的通信波形或通信環境波形數據以MDMA方式傳送到通信/通信信號環境波形數據存儲器(SDRAM1)。同時將噪聲數據以SPI MDA方式傳送到DSP2的內部RAM中,然后在DSP2接收后,將噪聲/干擾數據以MDMA方式分別存儲到噪聲/干擾數據存儲段(SDRAM2)內。DSP1通過SPI非DMA方式傳送信噪比/干信比參數到DSP2的內部RAM中。其中通信數據的高位(D15)為基帶碼流數據,D14為同步信號,用于測試基帶碼流。

系統中,所有波形參數的采樣頻率為10MHz,數據容量為16 M×16位,可存儲1.5秒鐘的波形數據。數據有效位數為14位。DSP1通過PPIDMA方式直接從SDRAM1中循環讀取通信波形數據傳送給DAC1,產生通信波形。DSP2利用程序產生隨機地址,得到MDAM0的起始地址,然后將存儲的噪聲波形數據從SDRAM2中讀入DSP2內部RAM中,并且根據信噪比在內部RAM中進行幅度加權,然后通過PPI DMA傳送給DAC2,產生噪聲波形。若包含干擾信號,DSP2需要通過MD-MAl將干擾數據讀入內部RAM,并根據干信比在內部RAM中進行幅度加權,然后和噪聲疊加,再通過PPI DMA輸出到DAC2來產生干擾與噪聲的混合波形。其中PPI時鐘PPI_CLK信號均由各DSP的定時器產生。

兩個DAC的位數是14位,并且設置為4倍插值方式,即DAC輸入數據率為10MSPS,輸出轉換速率為40MSPS。DAC轉換需要的時鐘與PPI_CLK共用,DAC連接在BF533PPI總線的低14位PPI13~PPI0。基帶碼流通過DSPl的PPI15引腳輸出,同步信號通過DSP1的PPI14引腳輸出,經過74AC11244驅動輸出波形。

DAC輸出的模擬信號后經過AD8054緩沖放大,再經信號和噪聲合成后分為兩路,可作為測試波形和信號源。

若需要模擬通信信號環境,需要在微型計算機中計算多種信號的疊加數據,然后傳送到通信/通信信號環境數據存儲器(SDRAM1)中,其它過程均與通信方式相同。此模式下不能測試基帶碼流,但仍可測試同步信號。

數字通信相關文章:數字通信原理

評論