基于ADSP TS201的雷達信號處理機設計

2 雷達處理機實現

2.1 硬件平臺設計

系統運算量及時間要求,信號處理板需采用多DSP并行處理的結構,為達到高速浮點處理能力、高數據吞吐率及大內存空間的要求,DSP芯片選用ADSP-TS201,它是ADI公司最新型號的TigerSHARC架構高性能浮點數字信號處理器。它具有最高達600 MHz的工作時鐘,且每周期可完成4條指令;包括雙獨立運算模塊及用于地址計算的雙獨立整型ALU,可完全并行操作;擁有24 MB/s的片內存儲器,內存容量大;此外還有14路DMA控制器及外部端口、4個鏈路口,可進行高速數據吞吐;擁有4個SDRAM控制器,可外部擴展存儲芯片;擁有4個可編程flag引腳,可對外輸出所需標志信號。

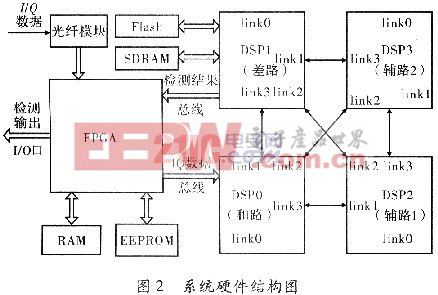

多DSP設計通常有共享總線方式和鏈路口耦合方式兩種結構。共享總線結構的優點是可以提供全局地址空間,把多DSP的地址空間映射到主機的內存空間進行統一訪問。任一DSP也可通過總線讀寫其它處理器內存,操作方便。然而,當多DSP間數據交換頻繁時,總線競爭往往造成數據通信的總線瓶頸,因而該方法有明顯的缺點。采用鏈路口耦合方式則具有明顯的優點,各DSP總線獨立,擁有完全獨立的內存空間,各DSP程序設計可完全獨立,減小了程序調試的難度。各DSP之間僅通過鏈路口無縫連接,片間連線少,降低了PCB布線難度和層數,節約了制板成本。此外,數據傳輸采用鏈路口的DMA方式并不占用DSP內核的運算時間,可以提高處理板的實時性能。因而采用將4片ADSP-TS201通過鏈路口兩兩互連,形成松耦合的多DSP結構,如圖2所示。各DSP通過鏈路口可在任意兩個DSP之間進行最高達500 MB/s的數據傳輸。

板卡主要以4片TS201與1片FPGA為核心,外加Flash,SDRAM與光纖及其配置芯片協同完成數據存儲及傳輸。FPGA主要完成系統中與雷達匹配的時序控制,對板外的數據傳輸與對DSP的總線通信。FPGA通過兩套獨立的32位外部數據總線與DSP0和DSP1連接,采用流水協議,外部總線工作頻率為50 MHz,可以實現400 MB/s的數據傳輸速度,達到了系統可進行高速數據傳輸的要求。系統時鐘為50 MHz,TS201經12倍頻工作在600 MHz,單板卡的系統峰值處理能力可以達到14.4 Gflops,板卡運算速度滿足了系統需求。

評論