基于Wishbone總線的UART IP核設計

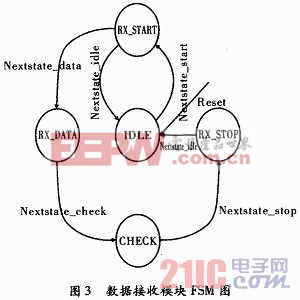

設計采用接收狀態機控制整個模塊的接收過程。接收狀態機可分為5個狀態,即IDLE、RX_START、RX_DATA、CHECK、RX_STOP,它們之間的狀態轉移,如圖3所示。本文引用地址:http://www.104case.com/article/156564.htm

IDLE狀態:當產生復位信號或運行至停止狀態之后,接收狀態機將復位到這種狀態。處于IDLE狀態時,它等待外部傳來的信號從高向低轉變,此時視為產生了一個有效的起始位。一旦有效起始位被檢測到,有限狀態機就會切換到下個狀態。

RX_DATA狀態:當狀態機跳轉到此狀態時,采樣每得到一位數據,就把接收到數據放到準備好的接收移位寄存器中。在設計中需要一個接收計數器來進行計數。當計數器提示數據接收已完成,則狀態機會轉入下個狀態。

CHECK狀態:當處于CHECK狀態時,通過對實際接收到的數據進行判斷得出實際數據的奇偶性,然后再與發送過來的數據的奇偶校驗位進行奇偶校驗。

如果符合,那么表示接收數據有效,可以傳入處理器;如不符,則不傳,直接丟棄數據。

RX_STOP狀態:無論停止位長度設定為1位或者是2位,有限狀態機總是等待1位樣本的采樣時間,然后抽樣停止位。只要一個邏輯采樣停止位被檢測到,數據接收模塊就不會去檢查是否停止位的配置出現錯誤。此時,有限狀態機將返回IDLE狀態。

2.3 數據發送模塊設計

發送模塊將從處理器接收到的數據,加上起始位,奇偶檢驗位和停止位組成規定的格式后串行輸出。首先,利用緩存器FIFO存放需要發送的數據,這樣處理器可以一次往FIFO中寫入多個字節的數據。發送數據時依次從FIFO中每次取出1Byte進行串行輸出。

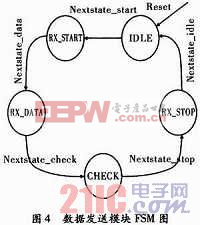

設計采用發送狀態機來控制整個模塊的發送過程。發送狀態機由以下5個狀態組成:IDLE、TX_START、TX_DATA、CHECK、TX_STOP,它們的轉移關系如圖4所示。

IDLE狀態:在沒有接收到將要發送的數據時,發送模塊一直處于該狀態,此刻一直保持發送模塊的數據位為高,當得到主機發出的工作信號時,發生狀態跳轉,進入下個狀態。

TX_START狀態:發送模塊會先發送一個數據“0”,作為起始位。起始位傳送完畢后,轉入下個狀態。

TX_DATA狀態:發送完起始位后,接著發送由主機傳來的有效數據。首先把數據存入模塊內的移位寄存器中,利用移位寄存器實現并行輸入到串行輸出的轉換。同時計數器開始計數,在發送完8位數據后,計數器清零,FSM隨即跳入下個狀態。

評論