基于Wishbone總線的UART IP核設計

2 UART IP核的設計實現

UART IP核的研發是遵照RS232協議和Wishbone總線標準進行的,集成了UART的基本功能。

UART IP核的主要技術特征包括:

(1)支持標準RSR232接口標準和Wishbone總線規范。

(2)全雙工獨立收發功能。

(3)接收通道進行奇偶校驗,溢出,產生可選中斷。

(4)內置支持接收和發送的16 Byte FIFO。

(5)發送“空”產生可選中斷,接收“滿”產生可選中斷。

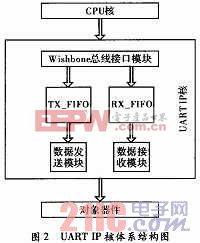

UART IP核體系結構如圖2所示。本文引用地址:http://www.104case.com/article/156564.htm

UART IP核內部主要包括數據發送模塊、數據接收模塊以及Wishbone總線接口模塊。各模塊的設計如下。

2.1 Wishbone總線接口模塊設計

Wishbone總線接口模塊將UART IP核與微機系統相連。該模塊提供Wishbone Master和Wishbone Slave接口。

Wishbone總線接口模塊的主要功能如下:

(1)提供UART IP核與其他設備的接口,如存儲器或者主機的接口。

(2)包含緩沖描述符(儲存于內部RAM)。

(3)包含信號在主機時鐘、發送時鐘和接收時鐘之間的同步邏輯。

(4)發送功能。讀取發送緩沖描述符,讀取數據到發送FIFO并開始發送,其后將發送狀態寫到發送緩沖描述符。

(5)接收功能。讀取接收緩沖描述符,將獲得的字節寫入接收FIFO,其后通過Wishbone Muter接口與微機系統進行通信。最后,將接收狀態寫到接收緩沖描述符。

當處理器需要串行發送數據時,先將數據以包的形式存儲于主存儲器中,然后將存儲的所有包的起始地址、目的地址、長度以及發送控制信息寫入發送描述符中。

Wishbone接口模塊讀取到一個非空的發送描述符后即發送數據,發送的數據要通過Wishbone接口邏輯訪問位于總線上的主存儲器,讀取到的數據首先放到發送FIFO中,其后再通過發送控制和同步邏輯與數據發送模塊進行握手,將數據從TX_O端口串行發送出去。

當接收數據時,數據由RX_I端口串行地移入接收FIFO中,每收滿8位數據就移入接收保持寄存器,然后通過Wishbone總線并行傳輸給處理器核。

2.2 數據接收模塊設計

由于外部信號是通過異步串行的形式傳輸,因此當接收端口檢測到一個由高到低的數據就被視為一個幀的起始位。為了避免接收信號的噪聲而產生的不正確的數據,檢測到的起始位時鐘至少要低于50%的波特率時鐘。接收模塊一旦接收到有效的起始位,就將通過RS232標準的波特率對數據位和校驗位進行采樣。

評論