基于機器視覺的嵌入式高速圖像通信系統設計

1 引言

隨著現代的圖形采集技術發展迅速,各種基于ISA,PCI,USB1.1等總線的圖形采集卡速度已經不能滿足用戶的需求,而采用 USB2.0以后就可以解決這個傳輸速度上的瓶頸,USB2.0的速度是480Mbits/s,完全可以滿足圖像采集、傳輸以及后續處理的要求。系統中采用 DSP+CPLD的硬件設計方案,采用現場可編程芯片 CPLD及兩片 SRAM構成的圖像采集和存儲系統,可以根據不同的需要進行現場編程,具有通用性好、價格相對便宜,易于系統調試,升級等特點。系統中 CPLD選擇的型號是 ALTERA公司的MAX7000系列低功耗芯片EPM7128A。片外大容量 SRAM是DSP與 CPLD的聯系橋梁,系統設計也利用這座橋梁將 USB和 CPLD有機地聯系起來。該系統的市場調查表明,適應于各種主動或被動的監測場合,以及醫療、公安和工業檢測當中。 2 系統的硬件設計方案

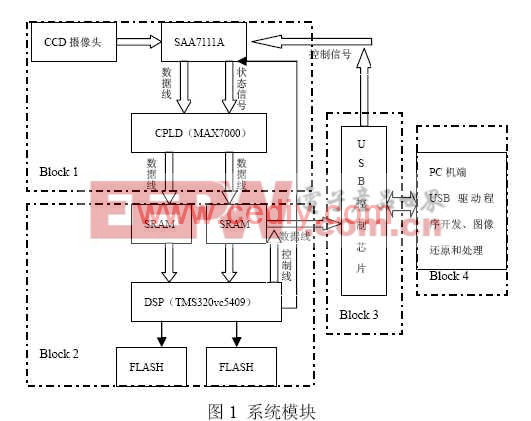

圖像通信系統包括以下四個部分,如圖 1所示:

(1) 圖像采集模塊,由線陣 CCD、CCD 驅動信號增強電路、CPLD 和 A/D 組成,用于采集圖像信號,并將模擬信號數字化,以便 DSP 處理。本系統采用黑白高速線陣TH7814A,該 CCD 為雙路輸出,像敏單元尺寸7 µm,最高驅動頻率 50 MHz;CCD 驅動信號增強電路是為滿足該 CCD 所需的 9 V 高速驅動而設計的;A/D 芯片采用 SAA7111A,它由雙通道模擬預處理電路、自動鉗位和增益控制、時鐘產生電路、數字多標準譯碼器色度/飽和度/對比度控制電路、彩色空間矩陣和 27MHz數據處理通道七部分組成,并由 DSP模擬I 2C總線進行時序配置,以上器件同步驅動脈沖均由 CPLD 產生。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論