基于NiosII處理器的通用AD IP核的設(shè)計(jì)與實(shí)現(xiàn)

2.2 FIR濾波器模塊的設(shè)計(jì)

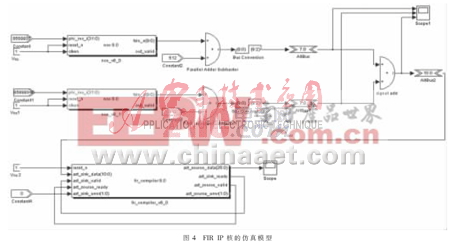

在實(shí)際應(yīng)用的數(shù)據(jù)采集系統(tǒng)中,往往需要對(duì)外界模擬輸入信號(hào)進(jìn)行濾波,以提取信號(hào)中有用的信息。在本設(shè)計(jì)中這部分的功能是由FIR濾波器模塊來完成的。FIR濾波器模塊采用Altera公司提供的FIR IP核來實(shí)現(xiàn),通過Simulink軟件中的DSP Builder工具對(duì)其進(jìn)行仿真并最終可以生成底層HDL代碼。由于TLC549的最高采樣頻率為40 kHz,本文設(shè)計(jì)了一個(gè)低通濾波器,它的采樣頻率為40 kHz,3 dB截止頻率為100 Hz。在Simulink軟件中建立的FIR IP核的仿真模型如圖4所示。本文引用地址:http://www.104case.com/article/151966.htm

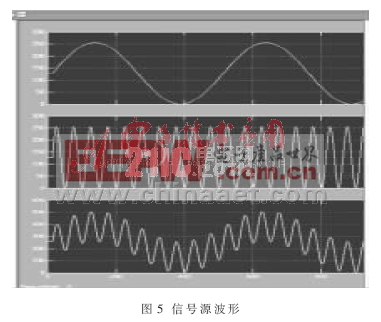

圖4中nco_v8_0模塊和nco_v8_1模塊是2個(gè)數(shù)控振蕩器,分別用于產(chǎn)生100 Hz和1 kHz的正弦信號(hào),signal add模塊是并行加法器,它將兩路正弦信號(hào)進(jìn)行疊加并將和信號(hào)輸出。fir_compiler_v8_0模塊是FIR IP核,它將signal add模塊輸出的和信號(hào)作為輸入,并將數(shù)字濾波的結(jié)果輸出到示波器進(jìn)行顯示。仿真結(jié)果如圖5和圖6所示。

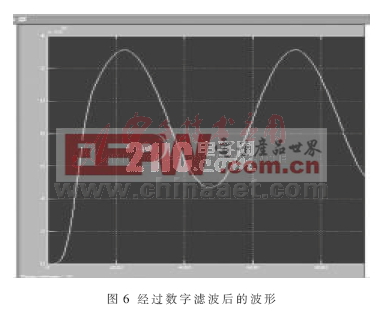

由圖5可以看出:第1路是頻率為100 Hz的正弦信號(hào),第2路是頻率為1 kHz的正弦信號(hào),第3路是前兩路信號(hào)的疊加。圖6中顯示的是經(jīng)過數(shù)字濾波后的波形,可以看出只有100 Hz的頻率分量存在,1 kHz的信號(hào)被濾除了,從而完成了對(duì)FIR IP核的功能驗(yàn)證。通過圖4中的Signal Compiler工具可以完成該FIR IP核的底層HDL代碼的生成。

FIR濾波器模塊采用Altera公司提供的FIR IP核來實(shí)現(xiàn),具有高性能、可配置、可重用等特點(diǎn)。設(shè)計(jì)者只需根據(jù)整個(gè)系統(tǒng)的需求以及所選用AD芯片的采樣速率等參數(shù)確定濾波器的類型與系數(shù),并對(duì)該IP核進(jìn)行參數(shù)化、實(shí)例化,即可完成針對(duì)該款AD芯片的FIR濾波器模塊的設(shè)計(jì)。因此這部分的設(shè)計(jì)對(duì)于不同的AD芯片是相對(duì)獨(dú)立的,具有很好的通用性。

2.3 FIFO緩存模塊的設(shè)計(jì)

為了連續(xù)和正確地采集數(shù)據(jù),實(shí)現(xiàn)無縫緩沖,本設(shè)計(jì)利用了FIFO做數(shù)據(jù)緩存。由于TLC549是8位的AD芯片,故本設(shè)計(jì)采用1個(gè)512×8 bit 的FIFO來存儲(chǔ)采樣的數(shù)據(jù)。當(dāng)FIFO中的數(shù)據(jù)存滿時(shí),它會(huì)向Nios II CPU產(chǎn)生一個(gè)中斷信號(hào)。頂層應(yīng)用程序可以通過中斷服務(wù)程序?qū)IFO中的數(shù)據(jù)讀到內(nèi)存中進(jìn)行處理。這樣既不會(huì)造成數(shù)據(jù)的丟失,同時(shí)可以保證CPU較高的效率,很好地解決了上述的速度不匹配的問題。

FIFO緩存模塊的設(shè)計(jì)對(duì)于不同的AD芯片是相對(duì)獨(dú)立的,設(shè)計(jì)者只需根據(jù)所選用AD芯片的精度、采樣速率、時(shí)鐘速率等參數(shù)確定FIFO緩存的位寬和深度,并對(duì)FIFO進(jìn)行參數(shù)化、實(shí)例化,即可完成針對(duì)該款A(yù)D芯片的FIFO緩存模塊的設(shè)計(jì),因此具有很好的通用性。

評(píng)論