在32位CPU中Load Aligner模塊數據通道的設計與實現

設計目標

本文引用地址:http://www.104case.com/article/151737.htm本設計中,Load Aligner模塊要實現的指令有LB、LBU、LH、LHU、LW、LWL、LWR。CPU通過這些指令把從數據存儲器中取出來的數據重新排序,然后放進寄存器堆RF中,進入CPU的數據通道。表1是對這些指令的介紹。

如果把從DCACHE中取出的一個32位的字表示成4字節:A、B、C、D,如表2所示。

31-24/ 23-16/ 15-18/ 7-0

A / B / C / D

那么經過上述指令操作后,這個字被重新排列的結果(即Load Aligner模塊的輸出,也用4字節來表示)見表3。

表3中,s表示符號擴展,*表示這個字節上的寄存器中的數保持不變。不過在Load Aligner模塊,先將這些字節置0,在寄存器堆模塊再控制這些字節是否直接寫進寄存器。

以上是Load Aligner模塊要實現的指令目標,另外由于此模塊是CPU關鍵路徑的一部分,因此數據通道部分最長時延不能超過0.7ns。

邏輯設計

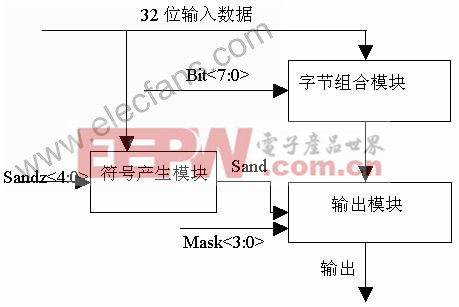

分析比較經過上述指令后Load Aligner模塊的輸入輸出變化可以看出:輸入字的每一字節經過Load Aligner模塊后可以在輸出字的任意字節位置上。換言之,輸出字的每一字節都可以有A、B、C、D四種情況。所以需要一個8位的控制信號Bit7:0>來控制四個四選一的數據選擇器,稱為字節組合模塊,來獲得所需要的字節組合。不過,經過這個字節組合模塊選出來的4字節并不全是所需要的,還需要去掉冗余的字節或者進行符號擴展。因此需要有能夠產生符號擴展或者0擴展的模塊稱為符號產生模塊,然后把它的輸出和一個4位的控制信號Mask3:0>一起控制一組二選一數據選擇器,稱為輸出模塊,來獲得最后的排序結果。邏輯實現流程圖見圖1。

評論