基于DSP的動態稱重系統設計

(4)TMS320C6416信號處理模塊

該模塊采用高性能的TI公司的TMS320C6416DSP芯片負責數據的采集和處理。TMS320C6416是目前能力最強大的處理器(DSP),它的主頻高達600 MHz,內部包括1個DSP內核、一級數據Cache、一級程序Cache、二級存儲器、增強型DMA控制器(EDMA)、Vterbi譯碼協處理器(VCP)、T-urbo譯碼協處理器(TCP);對外接口包括2個外部存儲器接口(EMIFA和EMIFB)、主機接口(HPI)、PCI接口、UTOPIA接口、多通道緩沖串口(McB-SP)。

TMS320C6416采用了兩級超高速緩存器,即16 KB的一級數據Cache、16 KB的一級程序Cache和1 024 KB的數據和程序統一內存。如果需要擴展緩存,1 024 Kb內存中的256 Kb存儲空問可設置用作二級Cache。在內存和外設接口(EMIFA接口、EMIFB接口、HPI或PCI接口、McBSP串口、UTOPIA接口等)之間所有的數據傳輸都由EDMA來處理。TMS320C6416的EDMA共有64個通道,每個通道的優先級都可編程設置,每個通道都對應一個專用同步觸發事件,使得EDMA可以被外設來的中斷、外部硬件中斷、其他EDMA傳輸完成的中斷等事件觸發,開始進行數據的搬移。 EDMA完成一個完整的數據搬移后,可從通道傳輸參數記錄指定的鏈接地址處重新加載該通道傳輸參數。EDMA傳輸完成后,EDMA控制器可以產生一個到DSP內核的中斷,也可以產生一個中斷觸發另一個EDMA通道開始傳輸。

(5)PCI接口模塊

該模塊采用PCI Technology公司的橋接芯片PCI9052。PCI9052是PLX技術公司繼PCI9050之后推出的低成本低功耗、高性能的總線接口芯片,通過該芯片可使多種局部總線快速轉換到PCI總線上。根據PCI規范,主設備和從設備的劃分本質上是確定數據傳輸雙方訪問與被訪問的能力和關系。在此,PCI9052只能由主機或擁有總線主控制能力的其他設備進行數據的讀寫操作,但由于其內部有64 B寫FIFO和32 B讀FIFO,使PCI9052的局部總線和PCI總線能互相獨立工作。PCI9052允許設計相對的低速局部總線在PCI總線上獲得132 MB/s的突發數據傳輸速度。

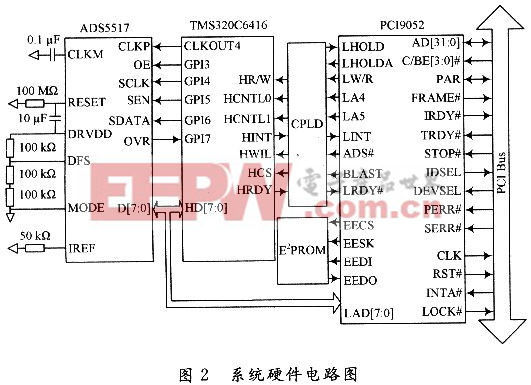

2.3 硬件電路

系統硬件電路圖如圖2所示。本文引用地址:http://www.104case.com/article/151478.htm

3 動態稱重系統軟件設計

系統的軟件設計由數據采集子系統、數據存儲管理子系統、稱重收費子系統三部分組成。軟件利用Delphi語言編寫,軟件具有友好的用戶界面,可方便地實現稱重數據的存儲、顯示。

3.1 數據采集子系統軟件設計

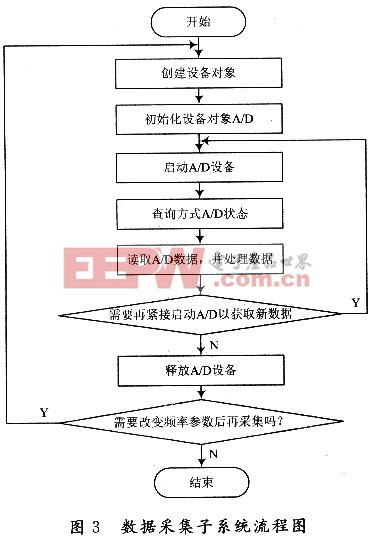

數據采集軟件設計的流程圖如圖3所示。

數據采集子系統軟件其主要功能包括實時采集稱重傳感器的電壓信號,并可調整數據采集速率,顯示測試電壓值,并保存現場數據。其中用戶界面如圖4所示。

評論