基于DDS的電路板檢測儀信號源設計

0 引言

某型導彈測試設備電路板檢測儀主要完成該測試設備的電路板的故障檢測。該檢測系統要求激勵信號產生電路體積小,配置靈活,且精度高、轉換速度快。基于FPGA的DDS信號發生器較傳統信號發生器能夠更好地滿足檢測儀要求。

直接數字頻率合成(Direct Digital Synthesize,DDS)是從相位概念出發直接合成所需波形的一種頻率合成技術。它是繼直接頻率合成和間接頻率合成之后發展起來的第三代頻率合成技術,突破了前兩代頻率合成法的原理,從“相位”的概念出發進行頻率合成,這種方法不僅可以產生不同頻率的正弦波、方波、三角波,而且可以控制波形的初始相位,還可以用此方法產生任意波形,目前得到了廣泛的應用。

1 DDS的工作原理和基本結構

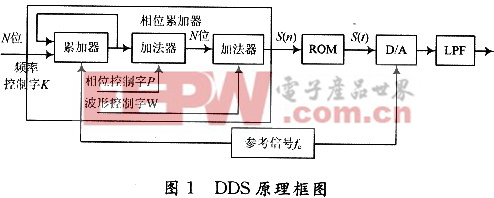

一個直接數字頻率合成器由相位累加器、加法器、波形存儲ROM、D/A轉換器和低通濾波器構成。DDS的原理框圖如圖1所示。

圖1中K為頻率控制字,P為相位控制字,W為波形控制字,fc為參考時鐘頻率,N為相位累加器的字長,D為ROM數據位及D/A轉換器的字長。相位累加器在時鐘,fc的控制下以步長K作累加,輸出的N位二進制碼與相位控制字P,波形控制字W相加后作為波形ROM的地址,對波形ROM進行尋址,波形ROM輸出D位的幅度碼經D/A轉換器變成階梯波,再經過低通濾波器平滑后就可以得到合成的信號波形。合成的信號波形形狀取決于波形ROM中存放的幅度碼,因此用DDS可以產生任意波形。

設頻率控制字是K,輸出頻率為f0,參考時鐘是fc,相位寄存器為N位,頻率分辨率是△f,則有:

通過頻率控制字的改變和寄存器位數的增加,可以得到令人滿意的頻率。

2 基于FPGA的DDS信號發生器的設計

該信號發生器是作為電路板檢測儀的激勵信號源,產生的信號分別為:頻率為16 000±0.8 Hz的正弦波,頻率為128 000±6.4 Hz,64 000±3.2 Hz,4 000±O.2 Hz的方波和周期為10μs,占空比為1:4的脈沖信號。下面以正弦波的產生為例說明DDS的實現過程。當f0=16 000 Hz,N=16時,根據式(1),則K=104。

2.1 相位累加器

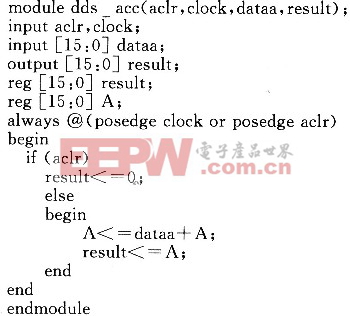

相位累加器主要是根據頻率控制字生成ROM查找表的地址,采用硬件描述語言Verilog DHL實現,其源程序為:

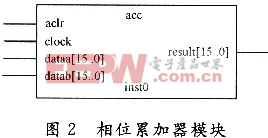

文本輸入完畢后,用QuartusⅡ進行編譯,然后生成.bsf文件,以便在頂層設計時調用。其生成頂層模塊如圖2所示。

評論