SoC設計之組態性處理器IP

5.針對SoC的應用進行最佳化

SoC的應用非常多,有的是數字相機(DSC)的SoC,有的是可攜式媒體播放器(PMP)的SoC,或是導航機(PND)的SoC,不同的SoC其應用設計也不同,例如DSC SoC不重視音訊處理,而PND SoC只專注靜態視訊處理及簡易的音訊處理,但卻需要重視數字信號的處理(接收衛星定位信號后的相關處理),至于PMP、STB(視訊機上盒)則重視動態、高質量的音/視訊處理,也重視信號處理(接收、處理節目信號)。

由上可知,不同的執行處理特性、不同的運算負荷度,若用單一架構處理器IP則難以滿足設計,而可組態性處理器IP卻可以針對不同的應用需求來進行組態,以合乎各種應用取向的SoC設計。

可組態性處理器IP的隱憂

雖可組態性處理器IP有如上的5種優點,但也不表示沒有缺點,事實上,隨半導體技術及市場演化,可組態性處理器也面臨一些隱憂、威脅,以下我們簡要討論。

1.工藝持續縮密,芯片面積資源獲得寬解

芯片的縮密工藝技術仍持續精進,從90nm、65nm、到45nm,并持續往下探,使芯片電路面積成本愈來愈低,因此芯片設計者已不如過往般重視面積成本,事實上處理器的多核化發展,無論是同質多核、異質多核,都表示「透過電路面積倍增的作法來爭取效能提升」已屬可行、值得。如此,透過組態作法讓執行核心的面積最佳化,此種需求將逐漸減少。

2.芯片上市的時間壓力愈來愈大

使用IP為的就是要節省芯片設計的驗證心力、加速芯片的開發,讓芯片更早上市銷售,而今市場競爭更加激烈,芯片Time To Market壓力比過去更大,使許多SoC項目都舍棄從Soft IP階段開始設計,直接取用Hard IP加速設計。

然而可組態性處理器IP可說是比Soft IP更Soft(軟)性的IP,是從「比Soft IP」更前期的設計階段開始著手,好處是獲得更高的設計彈性,但相對的就是增加SoC的設計時間,甚至為實現組態化而必須學習、熟悉另一套前期設計工具,即處理器的組態工具。

3.軟件風險

此點前面已約略提及,事實上,除有軟件移植性、兼容互通性等疑慮,軟件的后續維護也將令人擔憂,同時協力業者提供的宏程序(Macro)也可能無法立即適用,這些都須再行斟酌、調修。特別是軟件開發、維護成本在整體SoC方案中所占的比重愈來愈高,許多原有以硬件電路方式設計成的功效,而今多半轉成軟件方式實現。

4.固定組態處理器IP的轉向

ARM、MIPS等皆是以固定組態性處理器IP為主,不過為因應客戶需求也開始有些轉變,或允許部分的特例,例如MIPS的Pro系列IP就擁有組態性,或如ARM的OptimoDE Data Engines能因應不同需求的應用設計。

附注1:ARM、MIPS在處理器IP的主要授權業務逐漸成熟后,也開始進行相關延伸,如ARM延伸至實體IP領域,MIPS延伸到模擬/混訊IP領域,此外兩家業者皆開始跨入32位的控制器IP市場。

附注2:除了Soft IP、Hard IP外也有Firm IP,Firm IP的設計完成度介于前兩者之間,不過在產業的實際運用中卻不如前兩者普遍。

本文引用地址:http://www.104case.com/article/151474.htm

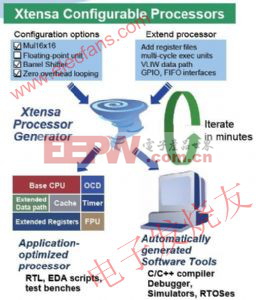

圖 Tensilica Xtensa系列可組態性處理器IP的組態設計示意圖,左上是勾核需求的功效項、特性項,例如需不需要硬件乘法器、桶式移位器等,右上則是延伸處理器架構,例如增加緩存器、增加VLIW數據路徑等,左下則進行設計應用最佳化,右下則是軟件自動化產生工具。

評論