基于ARM的可定制MCU可承擔FPGA的工作

如今的產品生命周期可能短至六個月,因此在這種情況下要想取得定制ASIC的低成本、低功耗和高性能優勢幾乎是不可能的。定制ASIC的設計周期通常要一年左右,這通常要比終端產品的生命周期還要長。另外,標準單元ASIC還具有NRE費用(非重復工程成本),對于基本的0.13微米設計,該成本約為30萬美元,而對于具有復雜IP內容的90nm設計將超過100萬美元。因而當每年的批量小于10萬片時,從經濟角度看就不具有可行性。

本文引用地址:http://www.104case.com/article/151377.htm為此人們研發出了平臺化或結構化ASIC,它們具有預設計的IP塊和可編程的ASIC門,可顯著降低成本并縮短設計周期。這種方案將設計周期從一年甚至更長的時間縮短到幾個月,還將NRE成本降低到大約15萬美元,不過與門陣列相關的較大尺寸使得單片成本過高而無法補償NRE。

利用現成的標準微控制器來實現設計通常會較快且具有較高的成本效益,許多微控制器都是系統級芯片(SoC),能夠提供大量的網絡功能和人機接口功能,例如LCD控制器和相機接口。這些現成的SoC常常具有所有功能,性能高且成本低,采用基于單元的ASIC即可實現。但是, 需要硬件加速的一些設計中要求一些高強度運算的功能,如Turbo編碼、GPS環形解調器和圖形處理等,它們都需要用硬件實現。未來發展趨勢是利用FPGA來實現這些DSP功能。由于工藝技術的進步,這種設計的成本將明顯降低,而且幾乎有完全取代平臺ASIC。

不過,FPGA也有一些缺點,最顯著的是功耗高,執行速度慢,FPGA中IP的安全性也相對較差。盡管其成本下降很快,但當批量達到1萬片時,其批量成本就不再下降了。因此FPGA還比較貴。

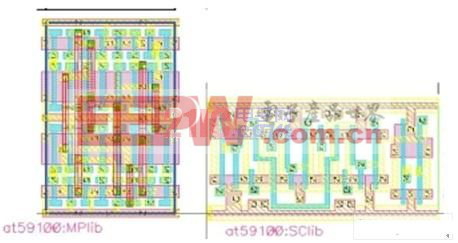

目前有種新的ASIC技術,它采用一種金屬-可編程的單元結構(MPCF),所實現的硅片效率與單元ASIC相當(在130nm工藝上為170K-210K門/mm2)。例如,在130nm工藝節點,利用MCPF實現一個D觸發器(DFF)所用的硅片面積與標準單元相比幾乎相同(圖1:用130nm MPCF和130nm 標準單元實現的D觸發器)。

目前正在利用MPCF技術開發可定制的微控制器,它不僅具有單元ASIC的超低單片成本優勢,還具備結構化ASIC的低NRE和不到兩個月設計周轉期的優點。基本上,具有SoC級集成度的現有MCU結合金屬化可編程單元結構就可用來實現可定制的SoC平臺。

作為這種可定制微處理器的一個例子,它采用了基于200 MHz ARM926EJ-S的現有MCU,帶有用于確定性處理且均為16 Kbytes的緊耦合程序和數據高速緩存,32 Kbytes的附加SRAM,32 Kbytes的ROM以及支持網絡、數據傳輸、人機接口的外設,并增加了一個等效于28K 或 56K FPGA LUTs (250K 或 500K 可布線 ASIC門)的金屬化可編程塊(MP)。(圖2- AT91CAP9方框圖)。器件上已有的外設包括USB 主機和器件、10/100 以太網MAC、LCD控制器、用于連接CAN、MCI和SPI總線的圖像傳感接口。

圖1:用130nm MPCF和130nm 標準單元實現的D觸發器。

評論