標(biāo)準(zhǔn)單元ASIC和FPGA的權(quán)衡及結(jié)構(gòu)化ASIC

多種制造FPGA的深亞微米工藝,如Xilinx公司最新Spartan-3系列產(chǎn)品采用的90納米工藝(參考文獻(xiàn)1),使每塊芯片上的門電路數(shù)量變得越來越大。如果您的設(shè)計(jì)使用FPGA的嵌入式存儲(chǔ)器陣列和擴(kuò)散式模擬及數(shù)字功能模塊,如DLL、PLL、乘法累加器、串行器/解串行器(SERDES)電路、高速I/O緩存器,在某些情況下甚至是CPU芯核和相關(guān)外設(shè),則FPGA的可用功能是極大的。您可以根據(jù)設(shè)計(jì)的需求來訂購(gòu)少量或大量的FPGA,而且不必向供應(yīng)商支付NRE(非經(jīng)常工程)費(fèi)用。供應(yīng)商已經(jīng)安排并調(diào)試芯片的邏輯平面、存儲(chǔ)器平面、信號(hào)路由平面以及電源平面。

一旦您的設(shè)計(jì)完成,你便可在幾秒鐘到幾分鐘之內(nèi)擁有一塊實(shí)用的芯片。一般說來,你用來開發(fā)和調(diào)試設(shè)計(jì)的工具要比用于開發(fā)調(diào)試專用集成電路(ASIC)的工具便宜許多。(然而,如果Hier設(shè)計(jì)公司售價(jià)為25,000 美元的PlanAhead代表未來工業(yè)趨勢(shì)的話,F(xiàn)PGA工具組的平均價(jià)格將會(huì)上漲)。但是,無論FPGA變得多么密集,F(xiàn)PGA的面積效率仍然要比用可比工藝制造的標(biāo)準(zhǔn)單元ASIC低一到兩個(gè)數(shù)量級(jí)。FPGA,尤其是基于占用大量硅面積的、每個(gè)單元六個(gè)晶體管的靜態(tài)存儲(chǔ)器(SRAM)的查尋表(LUT)和配置元件技術(shù)的FPGA,其功耗要比對(duì)等的ASIC大得多。

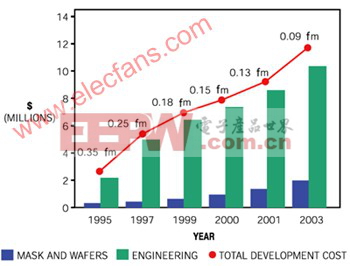

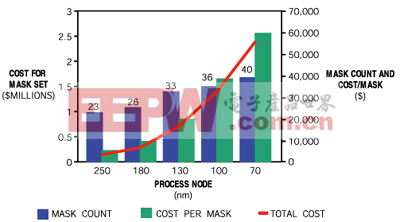

遺憾的是,ASIC的很多優(yōu)點(diǎn)也帶來相應(yīng)的缺點(diǎn)。由于芯片按照摩爾定律光刻線路發(fā)展,NRE費(fèi)用、最少訂購(gòu)數(shù)量以及每席開發(fā)工具套件的費(fèi)用都將猛漲(圖1)。ASIC的最少訂購(gòu)數(shù)量反映了供應(yīng)商能夠在生產(chǎn)線上生產(chǎn)并仍可獲利的最少的用戶專用晶圓。芯片的裸芯片越大,所需的最小訂購(gòu)數(shù)量就越小,而且您還會(huì)看到為什么改用線寬更小的光刻工藝和更大的晶圓后能大大提高這種最小批量需求。

圖1 標(biāo)準(zhǔn)單元ASIC掩膜集、非經(jīng)常性工程(NRE)和工具集三種費(fèi)用以指數(shù)形式增長(zhǎng),這驅(qū)使大量潛在用戶考慮各種替代辦法(由Altera公司提供)。

電源電壓下降、信號(hào)耦合以及深亞微米布線效應(yīng)會(huì)造成種種故障,查找、修理這些故障所需的時(shí)間加上布線主導(dǎo)的時(shí)序收斂,都會(huì)延長(zhǎng)標(biāo)準(zhǔn)單元ASIC的開發(fā)周期。甚至在當(dāng)您認(rèn)為您的設(shè)計(jì)業(yè)已完成時(shí),您還不得不等待設(shè)計(jì)通過漫長(zhǎng)的生產(chǎn)、測(cè)試以及包裝等工序,然后才能取回芯片,而且,如果您設(shè)計(jì)的芯片不工作或者不再能夠滿足快速變化的市場(chǎng)需求,那就會(huì)招致成本和時(shí)間延遲的成倍增加。用標(biāo)準(zhǔn)單元ASIC進(jìn)行設(shè)計(jì)需要大量的時(shí)間、勞力和金錢;正如最近的分析報(bào)告所指出的那樣,造成市場(chǎng)向FPGA急速轉(zhuǎn)移的就是這三個(gè)因素。但是對(duì)于門電路數(shù)量或芯片批量達(dá)到幾十萬(wàn)的設(shè)計(jì)或者對(duì)于性能要求或功率要求非常嚴(yán)格的設(shè)計(jì)來說,標(biāo)準(zhǔn)單元的ASIC仍然是唯一的技術(shù)選擇。

傳統(tǒng)的解決方案

對(duì)此怎么做出選擇呢?為了回答這一問題,首先比較一下FPGA和ASIC的基本硅標(biāo)準(zhǔn)組件,即兩者的邏輯單元和布線結(jié)構(gòu)。FPGA的邏輯單元都是粗粒的,從各種各樣的多路復(fù)用器和分立邏輯門到一個(gè)或多個(gè)LUT,全都是粗顆粒的,并且通常由觸發(fā)器作補(bǔ)充。Actel公司的 ProASIC FPGA目前能提供業(yè)界最細(xì)顆粒的邏輯模塊。FPGA供應(yīng)商設(shè)計(jì)其器件的內(nèi)部邏輯模塊布線,從而將所需的可由用戶配置的布線層數(shù)減到最少;這樣,設(shè)計(jì)編譯和布局布線軟件面臨的主要挑戰(zhàn)就是高效利用邏輯模塊問題。您得到的芯片具有大多未編程的邏輯模塊間布線資源;對(duì)于基于非熔斷閃存芯片來說,這些資源您可以在系統(tǒng)加電之前配置,而對(duì)于基于SRAM的FPGA來說,則可在系統(tǒng)啟動(dòng)之時(shí)及之后配置(如果您的設(shè)計(jì)支持的話)。

標(biāo)準(zhǔn)單元ASIC邏輯模塊與FPGA的邏輯模塊相比顆粒要細(xì)得多。顧名思義,“標(biāo)準(zhǔn)單元”都采用按相同標(biāo)準(zhǔn)尺寸來制造晶體管和芯片上的其他結(jié)構(gòu)。(這種同質(zhì)性就是標(biāo)準(zhǔn)單元與完全定制芯片的主要差異)。然而,正如“專用”這一名稱所示,ASIC的布局以及器件的時(shí)鐘、電源和信號(hào)布線都是您實(shí)現(xiàn)方法專用的。因此,芯片的金屬化層和多晶硅層對(duì)每個(gè)用戶來說全都是獨(dú)一無二的,而且供應(yīng)商在將器件運(yùn)送給您之前預(yù)先對(duì)布線進(jìn)行了配置,使您在系統(tǒng)生產(chǎn)和隨后的運(yùn)作過程中不必具備硬件定制能力。在這種情況下,開發(fā)軟件不是主要側(cè)重于使每個(gè)邏輯模塊內(nèi)的設(shè)計(jì)實(shí)現(xiàn)方法高效率,就像更粗顆粒的FPGA一樣,但卻要側(cè)重于邏輯模塊互連的高效率。

從歷史看,另一種ASIC——門陣列——介于FPGA和標(biāo)準(zhǔn)單元ASIC這兩個(gè)極端之間。與FPGA類似,門陣列的布線網(wǎng)格是通用而又預(yù)定的。和標(biāo)準(zhǔn)單元一樣,這種布線網(wǎng)格專門設(shè)計(jì)配置在芯片生產(chǎn)的最后幾個(gè)階段進(jìn)行,而且供應(yīng)商有時(shí)將細(xì)顆粒的邏輯單元陣列稱為“雙輸入‘與非’門之海”。近幾年,曾經(jīng)被廣泛應(yīng)用的門陣列已經(jīng)逐漸消失,隨著FPGA逐步蠶食其領(lǐng)地,門陣列已經(jīng)越來越明顯地成為萬(wàn)事通而無專長(zhǎng)現(xiàn)象的犧牲品。就從訂購(gòu)到使用的周轉(zhuǎn)時(shí)間而言,門陣列比標(biāo)準(zhǔn)單元快得還不夠,無法奪取大量FPGA的業(yè)務(wù)。而且,門陣列的性能和硅片面積效率太差,使它們無法取代很多標(biāo)準(zhǔn)單元。

掩膜

可編程FPGA

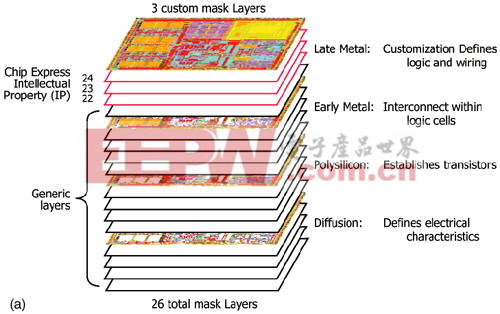

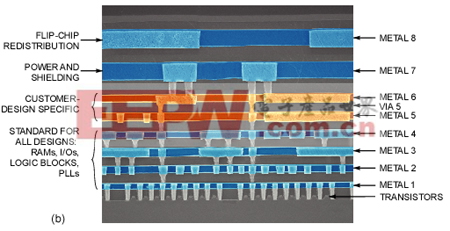

受到業(yè)務(wù)流失警示的一些ASIC供應(yīng)商把FPGA竅門寶典的一些經(jīng)驗(yàn)和門陣列的以往教訓(xùn)結(jié)合在一起,提出了結(jié)構(gòu)化的ASIC。有人也將這種方法稱為模塊化陣列或結(jié)構(gòu)化陣列。供應(yīng)商和供應(yīng)商之間存在大量的技術(shù)差別,但是簡(jiǎn)單的講,結(jié)構(gòu)化的ASIC是具有類似FPGA粗顆粒邏輯單元的門電路陣列派生產(chǎn)品,因而需要更少的可由用戶配置的金屬層和通孔層(圖2)。供應(yīng)商需要處理時(shí)鐘樹和電源平面布線。一個(gè)類比能夠有助于對(duì)結(jié)構(gòu)化ASIC設(shè)計(jì)的理解:在軟件編程的早期,微處理器的速度非常慢,存儲(chǔ)器非常昂貴,因此低級(jí)而又高效的匯編語(yǔ)言和更為低級(jí)的機(jī)器代碼占據(jù)了支配地位。

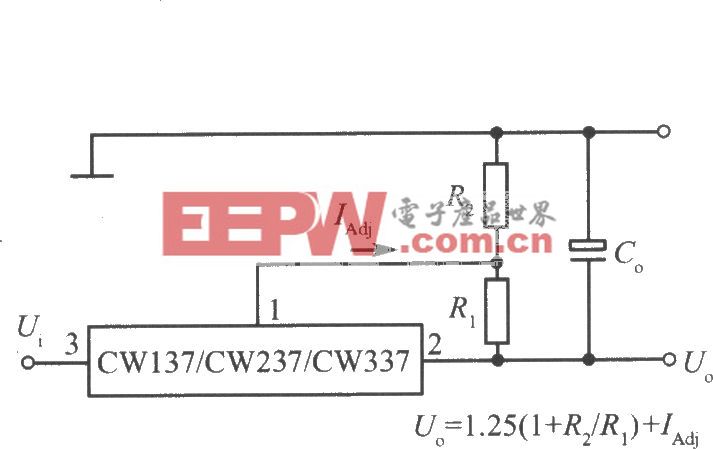

圖2 通過減少用戶專用掩膜的數(shù)量(a ,由ChipExpress公司提供)和金屬層和通孔層(b ,由Lightspeed Semiconductor公司提供),結(jié)構(gòu)化ASIC供應(yīng)商聲稱能增強(qiáng)其產(chǎn)品的靈活性并降低每個(gè)用戶的費(fèi)用。

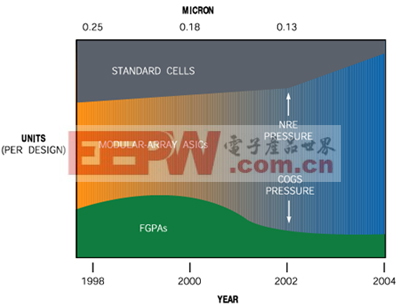

隨著CPU運(yùn)行速度的加快和存儲(chǔ)器價(jià)格的下降,更高級(jí)的軟件語(yǔ)言取代了以前的匯編語(yǔ)言和機(jī)器代碼。它們對(duì)資源的使用效率較低,但是好在現(xiàn)在效率并不顯得那么重要。然而,面市時(shí)間卻日益重要,而高級(jí)語(yǔ)言在這一方面出類拔萃。由于同樣的原因,VHDL和Verilog日益成為將電路變成芯片的硬件工程師們選擇的設(shè)計(jì)輸入方法,而更耗時(shí)的原理圖輸入技術(shù)則放棄使用。結(jié)構(gòu)化ASIC供應(yīng)商大膽地假定,將會(huì)出現(xiàn)一個(gè)硅平臺(tái)市場(chǎng),盡管硅平臺(tái)可能比標(biāo)準(zhǔn)單元的效率低,面市時(shí)間比FPGA長(zhǎng),但是也沒有那些競(jìng)爭(zhēng)產(chǎn)品的所有缺點(diǎn)(圖3)。因?yàn)樾酒难谀?mdash;—簡(jiǎn)便地說,常常也是最昂貴的掩膜——所占的百分比很大,這對(duì)于多個(gè)用戶設(shè)計(jì)來說是很普通的,所以每個(gè)用戶的NRE費(fèi)用就會(huì)減少,周轉(zhuǎn)時(shí)間就會(huì)縮短,而且你還能更容易地使由此產(chǎn)生的平臺(tái)適應(yīng)不斷演進(jìn)的工業(yè)標(biāo)準(zhǔn),和適應(yīng)硬件修改最少的派生芯片(圖4)。

圖3 結(jié)構(gòu)化ASIC廠商的陳述都用圖來表明他們的產(chǎn)品填補(bǔ)了標(biāo)準(zhǔn)單元ASIC和FPGA之間的空白。競(jìng)爭(zhēng)對(duì)手則聲稱結(jié)構(gòu)化ASIC芯片只不過是試圖使瀕臨死亡的門陣列復(fù)活,這種嘗試是注定要失敗的(由Lightspeed Semiconductor公司提供)。

評(píng)論