System C特點及FPGA設計

一、概述

SYSTEM C 是由 Synospy Inc. 提出的,目前最新的版本為V2.0。它提出的目的就是以一種系統設計的思想進行系統設計。它將軟件算法與硬件實現很好的結合在一起,提高了整個系統設計的效率和正確性。

System C 是一個C++ 庫,也是一種使設計者可以有效地設計出一個軟件算法的準確循環模型,硬件結構以及系統級設計的方法。 設計者可以用System C開發工具或在標準C++開發工具中加如System C庫制作系統級模型,快速地仿真和優化設計,以及研究不同的算法,并且為硬件和軟件設計人員提供一個設計系統的可執行規范。可執行規范本質上是一個C++程序,它顯示了和設計系統同樣的性能,為軟件設計人員和硬件設計人員提供了一個設計的標準。

System C 庫提供了創造系統結構模型的必須結構,包括那些在C++沒有的功能如硬件時序,并行和觸發功能。C++這種面對象語言提供了通過增加類來擴展語言的能力,而這種能力是C語言所不具備的。因此,System C使用大家熟悉的C++語言和開發工具。

二、SYSTEM C的特點

System C 支持對硬件和軟件的聯合設計,支持描述一個既包含硬件部分也包含軟件部分的復雜系統結構。它也支持對接口的描述,有以下幾個顯著的特點:

1.System C可以為軟件設計人員和硬件設計人員提供一個系統的可執行規范。設計人員使用該可執行規范可以避免設計中矛盾和錯誤的產生,并確保設計的完備性。這是應為在設計可執行規范時,系統設計者必須設計出也一個和系統具有同樣工作狀態的程序,通過這個程序可以發掘出潛在的矛盾和錯誤,并將這些矛盾和錯誤消除在整個設計的開始階段,而不是在整個系統進行調試階段才發現和解決這些矛盾和錯誤。這個程序還可以幫助設計者確保整個系統設計的完備性。

2.設計人員利用這個可執行的系統規范,還可以發現設計中概念模糊的地方。無論什么時候,設計人員對設計產生疑惑,就可以運行這個可執行程序以明確在這個問題上系統設計人員是如何處理的,從而確保系統設計的正確性。而現在的設計方法不能使設計人員方便迅速的解決這些疑惑。甚至這些疑惑是系統設計人員也不曾考慮過,這可能導致系統要重新進行設計。

3.在系統設計被實現以前,設計人員還可以通過用System C設計的系統可執行規范來驗證整個系統設計。這樣可以避免由于在系統設計上的失誤,而使系統實現不能達到要求。現在的設計方法不能提供這樣的手段在設計完成前進行系統的驗證,對系統的驗證必須是在系統設計完后。即使在完成前進行驗證,由于不能完全模擬實際系統的工作,其結果也只能作為一種參考。

4.System C設計的可執行規范所使用的TESTBENCH文件可以通過小范圍的修改或直接用在實現后的系統仿真。這就為設計實現人員帶來很大的好處,他們不必花很多的時間去編寫用來驗證實現后系統正確性的TESTBENCH文件。而現在采用的設計方法所使用的TESTBENCH文件卻沒有提供這樣的便利條件。這是應為軟件設計人員和硬件設計人員兩者的設計思想和設計手段都是不同的,一個軟件設計人員所使用的TESTBENCH文件并不能被硬件設計人員使用,甚至不能給硬件設計人員任何幫助。

三、SYSTEM C設計與傳統設計比較

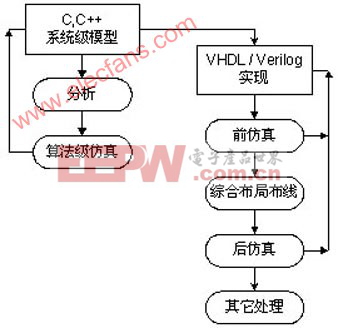

現在的系統設計一般是由系統工程師用C語言或C++語言設計出一個系統模型,并在系統級層次上檢驗概念和算法。當這些概念和算法被檢驗為正確無誤時,C/C++模塊被分解為功能相對獨立的子模塊。這些相對對立的子模塊由硬件設計人員手工地轉化為VHDL或Verilog語言用以硬件實現。這一個設計流程被顯示在圖1中。

圖1

從圖1所示的設計流程中我們可以發現以下幾個問題:

1.人工將CC++程序轉換為HDL程序容易產生錯誤。在現在的這種設計方法中,系統工程師先按期望的設計要求設計出一個C模塊,并驗證這個模塊使其達到期望的設計要求。然后系統工程師所設計的C模塊被硬件設計人員手工轉換為HDL模塊。這個轉換過程不僅容易產生錯誤,而且還很浪費時間。這是因為CC++語言和HDL語言有著顯著的區別。首先,HDL的處理方式比CC++的復雜。CC++程序采用順序執行的處理方式,而HDL程序中既有順序執行也有并行執行的處理方式。要將CC++程序轉化為HDL程序必然要引入一些控制信號,由這些信號控制HDL程序的運行,但這樣也容易產生錯誤。其次,CC++語言不涉及到時序關系。由于CC++語言不支持對時序的描述,系統工程師設計的系統模型只是驗證了概念和算法,而只能對時間耗費上有一個大概的估計。這就使得硬件實現時,為滿足系統在時間上的要求,硬件設計人員必須對軟件算法進行一定的改造或優化。而這些改造或優化也有可能引入各種錯誤。

2.系統模塊和HDL模塊間缺乏聯系。當系統模塊被轉換為HDL模塊后,HDL模塊成為整個系統設計的焦點。為適應硬件實現的特點,硬件設計人員會更改系統設計人員的設計,但這種更改只是在HDL模塊中進行,而系統設計人員設計的C模塊并沒有因此更改。這就使得系統工程師設計的C模塊和當前硬件設計人員設計的HDL模塊缺乏必要的聯系。當硬件設計人

員遇到概念模糊或理解錯誤的地方時,往往不能馬上從C模塊中得到明確的解答。此時,C模塊的設計人員也不一定能為HDL設計人員提供有效的幫助。

評論