基于FPGA的LTE系統(tǒng)中轉換預編碼的設計

2 總體結構設計

從表1中看出,LTE上行轉換預編碼要進行的FFT變換種類多,但每一種變換的架構是相似的,都是由基2及非基2點FFT的公共模塊組成。基2有點數(shù)為4,8,16,32,64,128,256的模塊,非基2的有點數(shù)為3,9,15,27,45,75,81,135,225和243的模塊,只要抽出這些公共模塊并精心設計,再合理地調用,就會順利完成這個看似繁瑣的工作。

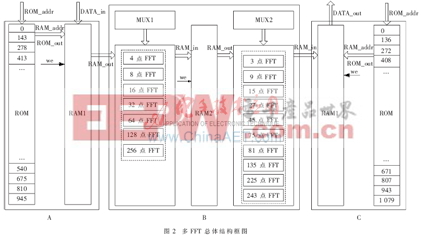

圖2所示總體結構框圖中,模塊A和C分別為數(shù)據(jù)輸入和輸出模塊;模塊B為數(shù)據(jù)處理模塊,其主要思想是動態(tài)配置和公共模塊的復用,內部FFT模塊事先單獨生成,MUX1,MUX2是選擇器,在不同輸入點數(shù)的情況下動態(tài)配置不同的內部FFT模塊來組合成外層FFT,這樣內部FFT模塊就可以達到復用的目的,可以大大減少總體資源耗用,而處理速度也與單獨執(zhí)行各FFT相當。

3 硬件實現(xiàn)

在實際應用中,一般由FPGA完成需要快速和較為固定的運算,由DSP完成靈活多變和運算量較大的任務[7]。Xilinx Virtex-5 SXT平臺針對具有低功耗串行連接功能的DSP和存儲器密集型應用進行了優(yōu)化,具有硬件結構可重構的特點,適合算法結構固定、運算量大的前端數(shù)字信號處理,可以大量卸載這些功能,釋放DSP帶寬以處理其他功能,所有這一切都使得FPGA在數(shù)字信號處理領域顯示出自己特有的優(yōu)勢。

3.1 地址映射

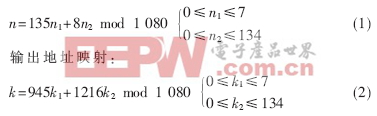

以1 080點FFT在圖2所示系統(tǒng)中的實現(xiàn)過程分析系統(tǒng)工作原理。因為1 080=8×135,且8和135互質,故外層采用Good-Thomas算法。

輸入地址映射:

FPGA內嵌Block RAM的使用可以大大節(jié)省FPGA的可配置邏輯功能塊(CLB)資源。Good-Thomas算法需要對輸入輸出數(shù)據(jù)進行排序,輸入輸出端處理方法相同,這里只介紹輸入端處理。在輸入端,鑒于Block RAM的特征,設置一個ROM和RAM,如圖2模塊A所示。對于不同長度的FFT,ROM不同,但RAM可以共用。在ROM里預先存放輸入數(shù)據(jù)在RAM1中的位置序號,此位置序號由(1)式得到,在時鐘沿到來時,先順序讀出存儲在ROM中的位置序號,將此數(shù)作為RAM1的地址輸入,就能將輸入數(shù)據(jù)存放到RAM1中的不同位置。這樣在輸入數(shù)據(jù)的同時完成了數(shù)據(jù)的排序,一舉兩得。1 080點FFT的輸入和輸出端地址索引如圖2所示,其邏輯時序圖見圖3。圖3中,RAM_in由測試數(shù)據(jù)xn_i和xn_r進行位拼接后輸入。

評論