JavaCard指令處理器的FPGA設計

3.5 Verilog表述的微碼處理器核心邏輯

下面是主控邏輯框架代碼的一部分。本段代碼體現了如何處理數據型微碼和指令型微碼,可以在YOUR_MICRO_CODE_INSTR處添加需要的微碼指令以及對應的操作。

always@(posedge clk or posedge reset)

begin

if(reset)

begin

new_mcp[15:0]=init_ADDR;//初始化微碼

//序列首地址

{pop,push,alu_calc,memrd,memwr,load_mcp,hold_mcp,remap_mcp}=8′b00000000;

H_READED=1′b0;//表示是否讀過了一次

//數據型微碼

state[1:0]=EXEC_MC;

end

else

begin

case(state[1:0])

EXEC_MC:

begin//首先根據mcr的位15判斷是數據型

//微碼還是指令型微碼

if(mcr[15])//mcr中存放微碼,位15==1表示

//此微碼是數據型,先保存高8位,再低8位

begin

if(H_READED==1′b0)//首個數據型

//微碼,數據保存到高8位

begin

{mcdata[15:8]}=mcr[7:0];

//mcdata是內部數據寄存器

H_READED=1′b1;

end

else

begin

{mcdata[7:0]}=mcr[7:0];

H_READED=1′b0;

end

end

else//表示此微碼是指令,根據后面的15位

//分支操作

begin

case(mcr[15:0])

YOUR_MICRO_CODE_INSTR://

begin

……//定義的微碼操作

end

……//其他微碼指令處理

endcase

end//end for mcr為指令處理

end

HLT://state[1:0]=HLT,宕機狀態處理

…

endcase//end for state[1:0]

end//end for reset

end//end for always@(posedge clk or posedge reset)

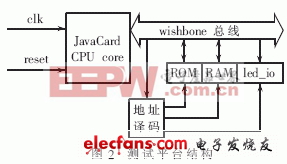

系統采用微碼實現,用微碼序列控制讀取Java指令、存儲數據,實現Java指令。JavaCard指令被解釋執行的過程如下:

讀取JavaCard PC處的JavaCard指令至指令寄存器Instr,發出remap信號給微碼指針調整模塊MCPC,微碼指針寄存器MCP得到新的JavaCard指令對應的微碼序列首地址,MCP的變化使微碼指令寄存器MCR變為該微碼序列的首個微碼指令,再由微碼處理器執行此MCR中的微碼。

評論