基于閃存的大容量存儲陣列

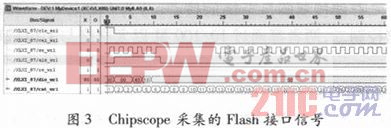

由Verilog HDL語言編寫模塊后編譯下載,用ChipSeope Pro采集到與NAND芯片的接口控制信號如圖3所示。本文引用地址:http://www.104case.com/article/149176.htm

圖3中信號是第一級存儲芯片的接口信號,是以cle_wrl的上升沿來作為觸發的,其中dio_wrl信號對應于上面編程時序圖的I/Ox信號,ale_wrl、cle_wrl、we_wrl、re_wrl、wp_wrl信號為Flash芯片的地址鎖存、命令鎖存、寫使能、讀使能、寫保護信號。其中寫命令h80后的00、40、1B是上位機通過控制板發至存儲板的行地址,由時序可知,與Flash芯片的所需要的編程時序一致。

3.2 流水的緩存模塊設計

根據NAND Flash芯片的特點,高速數據控制模塊的數據流按照頁訪問方式進行管理。設計選取的Flash芯片的頁大小為4 kB,因此在寫入的數據進入高速數據控制模塊后,首先進行按照頁大小進行數據分割。

在FPGA內開辟出40個容量為4 kB的雙口RAM的緩沖區,每10個為一組,相對應一組Flash陣列中的10片芯片。數據傳輸通道工作時序如圖4所示。

當數據率為200 MB·s-1時,數據傳輸周期是Tc1=5 ns,傳送1頁的時間是Tp1=4 096×Tc1=20.48μs,4級高速FIFO的延遲時間為△Tm=20 ns。在數據傳輸開始后,第1個10頁數據(P1,P3,P5,P7,P9,P11,P13,P15、P17,P19)以200 MB·s-1的速率分別寫入對應的存儲器組緩沖區G0,第2個10頁的數據以200 MB·s-1的速率分別寫入相應的存儲器組緩沖區G1,第3個10頁的數據以200 MB·s-1的速率分別寫入相應的存儲器組緩沖區G2,第4個10頁的數據以200 MB·s-1的速率分別寫入相應的存儲器組緩沖區G3。

評論