基于NAND Flash的數據存儲系統設計

3.3 FPGA配置電路模塊

本系統在FPGA配置電路中采用了主串配置模式。外部的配置芯片選用了XCF04S系列的PROM串行配置芯片。當系統上電時,芯片以主動配置方式來實現系統中FPGA的硬件配置。通過高速的串行接口,整個芯片的配置工作可以在很短的時間內完成。

3.4 電源模塊

電源模塊不僅能夠為系統各器件提供各種高性能的功率輸出,還能夠選擇合適的旁路、去耦電容來濾除各種干擾信號,保證系統的穩定工作。本系統電源模塊采用了TI公司的TPS75003芯片配置相應的外圍電路,實現了由5 V輸入電壓到3.3 V、2.5 V和1.2 V輸出電壓的精確轉換。

4 系統驗證與分析

在系統的軟硬件程序設計完成并生成BIT流文件后,下載到FPGA電路板上,結合PC機中的專用軟件對系統功能進行驗證測試。

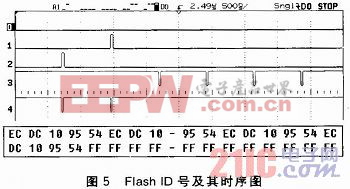

4.1 對NAND Flash的操作驗證

在數據存儲硬件系統設計過程中,用戶IP核設計得好壞決定著整個系統設計的成敗。系統IP核設計中集成了Flash控制器、DMA控制器以及數據和地址FIFO,為驗證該IP核是否能正常工作,對其進行了Flash操作驗證。示波器捕獲的讀Flash存儲器ID號時序圖如圖5所示。其中通道0~4分別代表Flash的CE(片選)、ALE(地址鎖存)、CLE(命令鎖存)、RE(讀)、WE(寫)信號。圖中Flash陣列的4片Flash的ID號都為EC DC 10 95 54,這與實際Flash ID相符。實驗證明,Flash存儲器的ID號是準確的。本文引用地址:http://www.104case.com/article/149111.htm

4.2 文件登記表驗證

實驗中在Flash存儲器的特定位置存有標記數據特征的文件登記表,應用程序讀取文件登記表中的信息并將相應數據傳輸到PC機上進行后期分析。文件登記表的存儲內容有:文件名、實驗的次數、存儲數據的長度、本次存儲的首尾地址以及下次存儲的首地址等。

圖6為某次存儲實驗的文件登記表信息,圖中前8個字節為文件名,往后依次為實驗次數和數據通道數。本次實驗中存儲的長度為50 MB,存儲首地址和存儲尾地址分別為0x0115、0x0178。由于所用的存儲策略為4片流水線式存儲,每片Flash每塊為128 KB,4片組成的模塊中每個大塊為512 KB(128 KB×4),所以可以計算出存儲的數據為512 KB×(0x0178-0x0115+1)=50 MB。這與所指定的本次存儲數據的長度吻合,表明存儲系統正確可靠。

評論