基于EPIC技術的可編程密碼處理器設計

輸入/輸出接口電路包括16個32bit輸入寄存器、16個32bit輸出寄存器、4個數據 長度計數器、1個32bit命令寄存器等,完成指令、運算數據從32bit數據總線裝載到指令存 儲器和輸人寄存器以及運算結果從內部通用寄存器寫入輸出寄存器等操作。本文引用地址:http://www.104case.com/article/148928.htm

3 指令系統設計

指令系統是算法要素和密碼處理器體系結構特性的集中體現,指令系統的設計必須支 持硬件的并行執行,即開發指令級并行性(ILP),指令級并行性的開發程度對發揮密碼微處理器的硬件特性,提高程序運行性能至為關鍵。ILP技術實際上是指一套完整的處理器設計和編譯技術,這些技術通過并行地執行獨立的機器操作(如存儲器讀寫、邏輯運算、算術運算等)來加速程序的執行。ILP的大小可以采用每周期平均執行的指令數(IPC)朱衡量,或者采用整個程序的每條指令平均執行的周期數CPI(CPT=l/IPC)來衡量。在可編程密碼處理器體系結構中采用了顯式并行指令計算結構,指令級并行數達到5。

3.1 指令分類

可編程密碼處理器體系結構中的指令分為以下幾類:

(1)靜態配置指令。它是在密鑰生成及加/解密過程中保持不變或者改變次數很少的控制信息配置指令,算法確定后,其S盒查找表信息、有限域乘數矩陣和不可約多項式、若干個置換的控制信息等就確定了,它們不會因為操作模式不同而改變。在加/解密過程中采用將配置指令分離出來的方法,可以大大減少執行密碼運算時指令的冗余編碼,從而縮短了指令字的長度,增加了運算指令字中包含有效操作的個數,有效地提高了加/解密速度并減少了密碼程序的代碼量。

(2)短指令。它執行除置換與128bit移位運算外的各種密碼運算和內部寄存器問的數據傳輸操作。

(3)長指令。它執行置換與128bit移位運算。

(4)超長指令。它執行立即數操作和多分支判斷操作。

(5)控制指令。它執行程序跳轉、子程序調用及返回、單分支判斷等控制操作。

3.2 指令形態

在硬件上,多個功能單元的設置為多條指令的并行執行提供了支持,而哪些指令可以并行執行,哪些指令不能并行執行以及如何將多條指令組裝成一條指令的原則,即稱為指令的拼裝規則。在此設計中有以下幾種指令形態:

(1) 靜態配置指令。

(2) 超長指令。

(3) 短指令Ⅱ短指令Ⅱ短指令Ⅱ短指令ll控制指令。

(4) 長指令Ⅱ控制指令。

其中短指令長度為37bit,控制指令長度為32bit,長指令長度為148bit。無論上述哪種形態,最終的指令字長度都為192bit(包括指令拼裝標識),如四個短指令可以與控制指令拼裝成一條指令,長指令也可以與控制指令拼裝成一條指令,但靜態配置指令與超長指令不能與其他指令拼裝,自身組成一個192bit的指令字。

4 性能分析

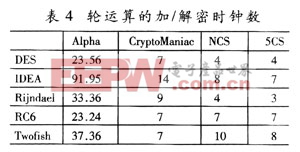

由于可編程密碼處理器體系結構支持5條指令綁定并行執行,因此其數據路徑定義為5CS(5Combining-Strands),假設不采用綁定的數據路徑定義為NCS(No-Combining-Strands),將這兩種情況與Alpha處理器、Cryp-toManiac密碼處理器[9]路程進行比較,四種數據路徑下加/解密所需時鐘數如表4所示。分析比較表明可編程密碼處理器執行時鐘大量減少,尤其與通用處理器Al-pha相比,加/解時鐘數DES算法減少83%,IDEA算法減少92%,Rijndael算法減少9l%,RC6算法減少69%,Twofish算法減少78%。

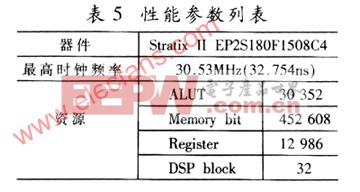

為了驗證可編程密碼處理器體系結構實現數據通路和控制通路的正確性,使用Altera StraTIxlIEP2S180F1508C4器件作為FPCA目標芯片,使用AlteraQuartusII 5.0工具進行綜合,在綜合前和綜合后使用Mentor公司的ModelSim 5.8c分別進行功能仿真和時序仿真,結果均正確。其具體資源占用情況如表5所示。

密碼處理的靈活性和高效性一直是密碼算法使用中的制約因素,采用通用微處理器雖然能獲得較好的靈活性,但卻使一些算法的性能達不到要求;采用專用算法芯片,在獲得很高性能的同時喪失了靈活性。本文針對這一矛盾以EPIC結構微處理器構架為出發點,系統地研究了通用的并行分組密碼處理器模型、各種密碼運算單元、指令集等關鍵技術,并最終得以實現,達到了實現性能與靈活性之間的良好折衷。

評論