基于FPGA處理器的數字光端機系統簡介

目前在高速公路、交通、電子警察、監控、安防、工業自動化、電力、海關、水利、銀行等領域視頻圖像、音頻、數據、以太網、電話等光端機開始普遍大量應用。

由于數字光端機具有傳輸信號質量高,沒有模擬調頻、調相、調幅光端機多路信號同傳時交調干擾嚴重、容易受環境干擾影響、傳輸質量低劣、長期工作穩定性差的缺點,因此許多大型重點工程已普遍采用數字光端機。

系統框架與工作原理

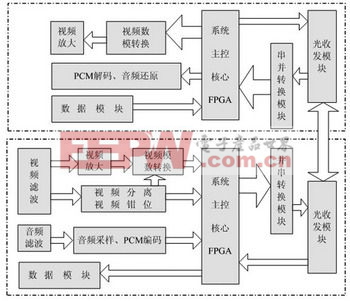

整個系統由核心控制模塊FPGA、音頻采樣編解碼模塊、視頻分離模塊、視頻放大模塊、視頻A/D和D/A轉換模塊、并串/串并轉換模塊、光纖調制收發模塊、電源控制模塊和485數據傳輸模塊。圖1是該系統的系統框圖。

圖1 系統結構框圖

系統的工作原理為:光端機系統分為兩部分,分別為:發射機和接收機。在發射端,來自監視器或其他視頻源的視頻信號首先經過發射板上的視頻濾波網絡去除噪聲干擾信號,然后對該視頻信號進行視頻分離和視頻放大。視頻分離模塊得到視頻信號的行、場同步信號以及奇偶場信號、視頻鉗位等重要的視頻信息。接下來,對放大后的視頻信號進行A/D轉換,得到的數字化的視頻信號送入系統主控核心FPGA中。與此同時,如果系統檢測到了有音頻信號的存在,則對其進行音頻濾波、音頻數字化采樣以及音頻PCM編碼。經過PCM編碼后的音頻信號,送入系統主控核心FPGA中。反向數據傳輸主要是485信號,該信號也送入到FPGA。這樣,系統主控核心FPGA對來自不同模塊的視頻、音頻、數據等信號整合,時分復用地將各個信號編碼成8位并行信號流送入到并串轉換模塊。信號流經過并串轉換后變成高速的LVDS信號驅動光纖收發模塊以波分復用的方式完成了電/光變化和光發射。在光端機的接收端,經過以上的逆過程,完成對原始信號的恢復。

系統硬件組成

1 FPGA核心控制器

系統的核心控制部分是整個系統的心臟,為了滿足對高速、多路數據流的實時處理,要求系統核心控制器必須有較高的工作頻率和反應能力。其次,對于系統時分復用部分,為了信號的同步化,需要系統核心控制器內嵌RAM和FIFO等功能塊。此外,同時作為嵌入式系統,處理器必須有著低功耗的要求。目前,FPGA處理器已經遍及工業控制、消費電子產品、通信系統等各類產品市場。按照低成本、低功耗、小體積、多功能及較為強大的數據處理能力,Altera公司CycloneII系列的EP1C3144是一個非常好的選擇。

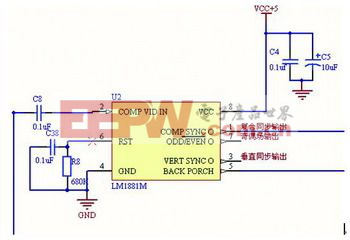

圖2 視頻分離硬件電路

2 視頻分離模塊

視頻信號中除了包含圖像信號之外,還包括了行同步信號、行消隱信號、場同步信號、場消隱信號以及槽脈沖信號、前均衡脈沖、后均衡脈沖等,因此,若要對視頻信號進行采集,就必須準確地把握各種信號間的邏輯關系。LM1881就是針對視頻信號的同步分離而生產的,它為視頻信號的處理提供了極大的方便。此處電路設計如圖2所示。

LM1881可以從0.5~2V的標準負極性NTSC制、PAL制、SECAM制視頻信號中提取復合同步場同步、奇偶場識別等信號,這些信號都是圖像數字采集所需要的同步信號,有了它們,便可確定采集點在哪一場,哪一行。LM1881也能對非標準的視頻信號進行同步分離,通過固定的時間延遲產生默認的輸出作為場同步輸出。

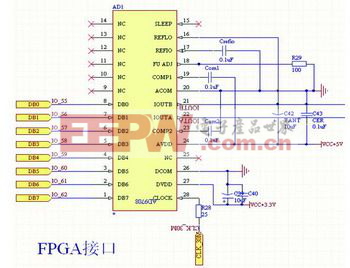

圖3 A/D轉換硬件電路

3 A/D和D/A轉換模塊

此處的A/D轉換電路主要用來對視頻濾波,放大后的視頻信號進行數字化變換。電視圖像信號的帶寬理論計算值為7.37MHz,實際取5.5275MHz。由香農定理知,ADC的采樣頻率應該大于2倍的圖像最高頻率,所以ADC采用ADI公司的AD9280,工作頻率為32MHz。該ADC具有良好的差分非線性度、模擬輸入超出轉換量程提示、內建自流電平回復和可調片內電壓基準源等優勢。

此處A/D轉換電路設計如圖3所示。

評論