為多處理器系統(tǒng)選擇最佳設(shè)計(jì)方案

過(guò)去開(kāi)發(fā)一個(gè)多處理器應(yīng)用,可能只需要寫下那些要求,核對(duì)一下那些大型DSP供應(yīng)商所供應(yīng)的器件的規(guī)格,然后選擇最好的芯片就可以了。但時(shí)代已經(jīng)變了,今天的工程師們有了更多的選擇。大型FPGA供應(yīng)商改進(jìn)了他們的信號(hào)處理產(chǎn)品,而選擇最佳方案則變得復(fù)雜。

本文引用地址:http://www.104case.com/article/148181.htm在本文中,我們將探討一下多處理器系統(tǒng)有什么可以利用的,以及如何在DSP、FPGA或者二者的混合方案之間作出最好的選擇。我們將分別簡(jiǎn)單地討論這兩種芯片,但將主要內(nèi)容更多地集中在系統(tǒng)級(jí)因素上。

對(duì)于高性能信號(hào)處理應(yīng)用,當(dāng)然還有除DSP和FPGA之外的其它選擇。ASIC和ASSP都能很好地適用于某個(gè)特定的信號(hào)處理應(yīng)用,但僅限于在大規(guī)模應(yīng)用中,否則它們的高成本都會(huì)讓它們無(wú)法成為優(yōu)選。

已獲認(rèn)可的DSP方案

自從20世紀(jì)80年代被發(fā)明以來(lái),DSP一直以合理的功耗和價(jià)格提供著優(yōu)越的性能。對(duì)于很多基于不斷快速改變的新興標(biāo)準(zhǔn)的應(yīng)用來(lái)說(shuō),DSP都很有吸引力。由于DSP算法可以很容易地以C語(yǔ)言等簡(jiǎn)單語(yǔ)言來(lái)執(zhí)行,就能在標(biāo)準(zhǔn)發(fā)生變化時(shí)更容易地對(duì)代碼進(jìn)行更新來(lái)反映這種變化。

另外,很多用于最新無(wú)線標(biāo)準(zhǔn)等應(yīng)用領(lǐng)域的信號(hào)處理算法的復(fù)雜本性,使之更適合利用DSP來(lái)執(zhí)行:一個(gè)DSP設(shè)備可以通過(guò)呼叫一個(gè)不同的軟件程序來(lái)更容易地改變處理算法。盡管現(xiàn)在的FPGA可以快速重配,但要在繼續(xù)處理數(shù)據(jù)的情況下動(dòng)態(tài)地實(shí)現(xiàn)這一點(diǎn),則是非常復(fù)雜且很有挑戰(zhàn)性的。

DSP在功耗方面也在不斷改進(jìn)。在手持設(shè)備市場(chǎng)的需求驅(qū)動(dòng)下,一些下一代高性能DSP結(jié)合了功耗管理技術(shù)。這可以讓整個(gè)系統(tǒng)的功耗在低數(shù)據(jù)量時(shí)得到降低,或者用來(lái)阻止過(guò)熱。一個(gè)功耗和溫度敏感型FPGA配置也能以相似的方式來(lái)管理其時(shí)鐘域,但需要更多的開(kāi)發(fā)工作。

但是,DSP并不特別適合并行處理:有些并行處理任務(wù)可能只需要一個(gè)FPGA,卻會(huì)需要多個(gè)DSP。比如,在無(wú)線基帶領(lǐng)域,對(duì)于WiMAX直角頻分多路存取(OFDMA)通道的處理來(lái)說(shuō),一個(gè)純DSP方案在所能處理的帶寬和通道數(shù)量上無(wú)法匹敵一個(gè)FPGA方案。因此DSP方案就會(huì)產(chǎn)生過(guò)高的成本和功耗。

靈活的FPGA方案

FPGA相比于DSP有一個(gè)很大的優(yōu)勢(shì):在并行應(yīng)用中的效率-這是通過(guò)采用多個(gè)并行處理區(qū)塊來(lái)實(shí)現(xiàn)的。FPGA擁有能讓嵌入式系統(tǒng)設(shè)計(jì)者將設(shè)備和應(yīng)用實(shí)現(xiàn)最完美匹配的靈活性,并能以每通道較低的成本達(dá)到最高的數(shù)據(jù)吞吐量。

FPGA雖然具有很高靈活性,但相比于硬接線式架構(gòu),它的門極數(shù)量和非優(yōu)化型方案的硅面積增加,因而在功耗上產(chǎn)生了額外的成本。但是,65納米技術(shù)和性能相當(dāng)?shù)腁SIC技術(shù)在量產(chǎn)中的應(yīng)用,讓FPGA不僅能在實(shí)驗(yàn)室環(huán)境中降低功耗,還能在量產(chǎn)中也將功耗進(jìn)一步降低。

盡管芯片層的功耗更高,但FPGA的通道平均功耗可以比DSP的低很多。DSP一般功耗只有3~4W,而FPGA的功耗為7~10W,但FPGA能處理相當(dāng)于DSP的十倍的通道密度。

近幾年來(lái),人們對(duì)DSP優(yōu)勢(shì)的推崇已經(jīng)轉(zhuǎn)變成為將FPGA和DSP技術(shù)結(jié)合起來(lái),比如Xilnx Virtex-5 SXT系列產(chǎn)品。這讓FPGA能夠結(jié)合DSP算法處理,執(zhí)行原本非并行的任務(wù)。這樣的“基于DSP”的FPGA在某些信號(hào)處理應(yīng)用中已經(jīng)顯示出了巨大的吞吐量?jī)?yōu)勢(shì),這一點(diǎn)通過(guò)其在高端處理市場(chǎng)的成功就得到了很好的反映。但是,F(xiàn)PGA一般不適合處理連續(xù)有條件型數(shù)據(jù)流。

編程FPGA仍然很難,一般需要一種偏向硬件的語(yǔ)言,例如Verilog或VHDL。FPGA方案的代碼會(huì)比DSP方案長(zhǎng)出數(shù)倍,這樣會(huì)增加開(kāi)發(fā)成本,并延長(zhǎng)上市時(shí)間。

基于C語(yǔ)言的合成工具還沒(méi)有實(shí)現(xiàn)C編碼式處理器方案的易用性和高性能。高級(jí)合成工具例如Simulink區(qū)塊圖合成目前還沒(méi)有得到廣泛應(yīng)用,而老的FPGA合成方法仍然延續(xù)著,尤其是當(dāng)需要最大性能時(shí)。

混合多處理器系統(tǒng)

從一個(gè)設(shè)計(jì)工程師的角度來(lái)講,F(xiàn)PGA和DSP的同步開(kāi)發(fā)讓他們能夠找到用于信號(hào)處理應(yīng)用的更新更好的方案。關(guān)于FPGA和DSP哪個(gè)更好的問(wèn)題并沒(méi)有一個(gè)簡(jiǎn)單的答案,而對(duì)于很多應(yīng)用來(lái)說(shuō)一個(gè)混合式系統(tǒng)才是最好的選擇。這個(gè)系統(tǒng)結(jié)合了兩種技術(shù)來(lái)提供一個(gè)方案,而這樣的方案要比二者單純相加要更好一些。

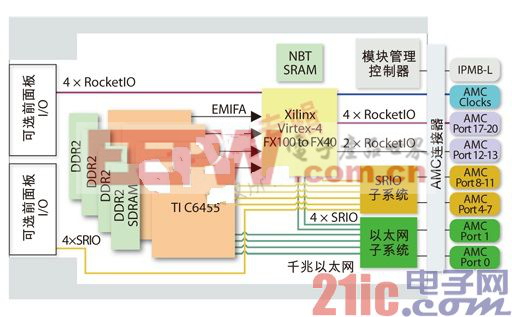

圖1展示了一個(gè)標(biāo)準(zhǔn)的刀片子系統(tǒng),其中包括了4顆TI公司的DSP和1顆Xilinx的FPGA。除了在DSP和FPGA之間采用EMIF連接來(lái)實(shí)現(xiàn)最小過(guò)空的協(xié)處理,這個(gè)子系統(tǒng)還帶有一個(gè)全Serial RapidIO (SRIO)架構(gòu),使其能夠用于無(wú)線電數(shù)據(jù)發(fā)送,并可用作卡上和卡外兩個(gè)設(shè)備間的一個(gè)低延遲直接內(nèi)存存取。

圖1:DSP/FPGA模塊(AMC-D4F1)架構(gòu)圖

先進(jìn)夾層卡(AMC)外形的可升級(jí)性貫穿了整個(gè)基架,尤其是當(dāng)系統(tǒng)以SRIO作為主要數(shù)據(jù)傳輸接口而構(gòu)建的時(shí)候。在先進(jìn)電信運(yùn)算架構(gòu) (ATCA) 或MicroTCA基架系統(tǒng)中,集成者都可以選擇混合并匹配以DSP為中心的刀片和以FPGA為中心的刀片,來(lái)實(shí)現(xiàn)恰當(dāng)?shù)募夹g(shù)平衡。

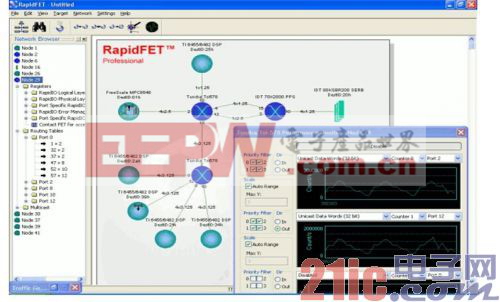

為了開(kāi)發(fā)高效的混合系統(tǒng),SRIP等協(xié)議以及AMC等標(biāo)準(zhǔn)讓設(shè)計(jì)者和集成者可以在刀片和系統(tǒng)兩個(gè)層面上把握平衡。圖2就展示了一個(gè)典型的混合系統(tǒng)。

圖2:采用RapidFET系統(tǒng)管理和分析軟件的SRIO系統(tǒng)軟件解析圖.

圖中可以看到終點(diǎn)和轉(zhuǎn)接點(diǎn)的結(jié)合。這個(gè)系統(tǒng)包含了CommAgility AMC-D4F1卡等各種卡。

在CommAgility,我們的目的是通過(guò)提供一套包含了多個(gè)FPGA或DSP的AdvancedMC來(lái)確保設(shè)計(jì)者能夠開(kāi)放選擇。這包括AMC-D4F1 (帶有4個(gè)TI的TMS320C6455 DSP和1個(gè)Xilinx的Virtex-4 FX系列FPGA)和AMC-D1F3(提供了1個(gè)DSP和3個(gè)FPGA)。這讓開(kāi)發(fā)人員可以根據(jù)其整體處理要求、應(yīng)用開(kāi)發(fā)和優(yōu)化階段以及有關(guān)DSP和FPGA的現(xiàn)有代碼庫(kù)的經(jīng)驗(yàn),來(lái)改變所用的技術(shù)。

將SRIO用到卡上和基架中讓各種元器件可以放到一起;AMC-D4F1利用了兩個(gè)4倍SRIO接口,提供了兩個(gè)高速的10Gbps鏈路,在MicroTCA,即將批準(zhǔn)的AMC.4規(guī)格將成為系統(tǒng)jigsaw中的最后一個(gè)部分,盡管它并沒(méi)能阻止目前已經(jīng)非常流行的SRIO AMC生態(tài)系統(tǒng)。目前已經(jīng)有多家廠商在提供SRIO支持,既支持MicroTCA網(wǎng)絡(luò)中心運(yùn)供應(yīng)商,還支持控制和信號(hào)處理AMC卡。

評(píng)論