異構雙核SoC設計與實現

摘要:異構雙核SoC采用SPARC V8處理器加專用DSP的架構,根據其應用特點,設計了SPARC V8處理器與專用DSP之間互斥通訊機制。并完成了SPARC V8處理器的狀態控制設計與優化、外部存儲控制器的接口優化設計,以及SoC的整體功能驗證。FPGA實驗結果表明,異構雙核SoC功能正確可靠,有效地提高了系統的效能比。

本文引用地址:http://www.104case.com/article/141887.htm引言

從開發并行性的級別來看,指令級并行是一種普遍存在于各類程序中的細粒度并行性,隨著片上集成度的不斷提高,再增加動態指令窗口的體積和發射寬度將無助于高主頻的實現,開發更高的ILP,以獲得整體性能的提升所需的硬件設計和驗證開銷已很難承受。單芯片多處理器(CMP)是近年來微處理器體系結構研究的熱點之一,它很好地解決了硬件設計和驗證復雜度提高的問題。在一些特殊應用領域使用通用的RSIC處理器來完成,需要較高的性能才能達到其基本要求,系統的效能比很低。如果采用RSIC核加專用DSP核的異構雙核結構,普通控制部分由RSIC核實現,特殊功能部分能夠采用專用的DSP來實現,可有效地提高系統的效能比,可明顯提升系統性能,同時有效降低整個系統的功耗。

異構雙核SoC設計與實現

異構雙核SoC結構

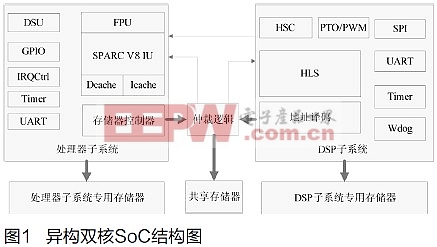

根據彈載測控系統的應用特點,采用RSIC處理器核加梯形圖解算專用DSP的異構雙核結構設計了SoC,如圖1所示。RSIC處理器核主要完成控制功能,負責系統的啟動,主程序的運行,狀態的查詢與傳輸,功能塊的運算,以及中斷的處理。專用DSP核主要完成梯形圖的解算、IO狀態表的刷新等工作。

RSIC處理器核采用經過多款芯片驗證的SPARC V8處理器核。處理器系統由整數處理單元、浮點處理單元、Cache子系統、中斷控制器、串口、定時器、看門狗、調試支持單元DSU等組成。在32KB指令Cache、16KB數據cache的配置下,采用Dhrystone2.1得出的運算性能可以達到0.86MIPS/MHz。

DSP核采用PLC梯形圖解算系統,該系統包含了HLS解算單元、定時器、串口、地址譯碼單元、PTO、PWM、SPI等模塊構成。

SoC運行方式

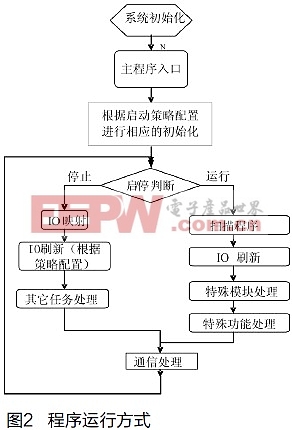

異構雙核SoC的主要運行方式如圖2所示,主程序在SPARC V8處理器中運行,對整個系統進行初始化操作,然后進入主程序,根據啟動策略配置進行相應的模塊初始化,接著進入無限循環調度程序。在無限循環調度程序中,判斷是否運行專用DSP;如果運行專用DSP,則暫停SPARC V8處理器的運行,將總線控制權交給專用DSP完成PLC掃描程序的運行、IO狀態的刷新、特殊功能處理,專用DSP完成一次順序掃描后將控制權交還SPARC V8處理器,SPARC V8處理器接著完成相應的通信處理,按IO映射表更新外部狀態;如果不運行專用DSP,SPARC V8處理器直接執行IO映射及相應的通信處理,按IO映射表更新外部狀態,然后重新判斷是否運行專用DSP,進行下一次循環。

評論