針對未來十年 “All Programmable”器件的顛覆之作

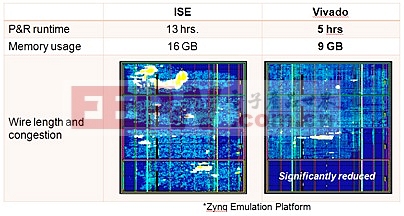

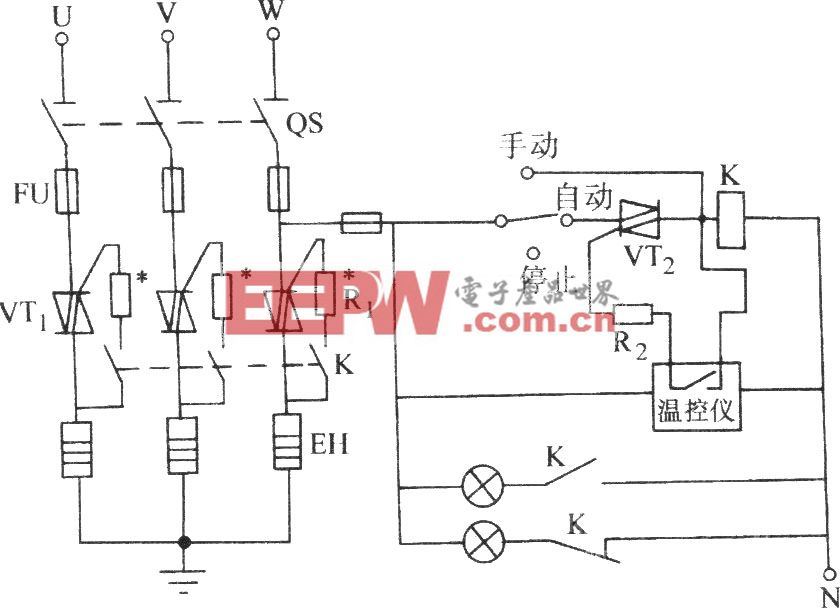

為展現這種優勢,賽靈思在 ISE設計套件和 Vivado 設計套件中用按鍵式流程方式同時運行針對賽靈思 Zynq-7000 EPP 仿真平臺開發的原始 RTL,同時將每種工具指向賽靈思世界最大容量的 FPGA 器件——采用堆疊硅片互聯技術的 Virtex-7 2000T FPGA。這樣 Vivado 設計套件的布局布線引擎僅耗時 5 個小時就完成了 120 萬邏輯單元的布局,而 ISE 設計套件則耗時長達 13 個小時(圖 2)。而且采用 Vivado 設計套件實現的設計擁塞明顯降低(設計中顯示為灰色和黃色的部分),器件占用面積較小,這說明總體走線長度縮短。Vivado 設計套件實現方案還體現出更出色的內存編譯效率,僅用9GB就實現設計要求的內存,而 ISE 設計套件則用了 16GB。

本文引用地址:http://www.104case.com/article/131872.htmFeist 表示:“從本質上來說, 你看到的就是 Vivado 設計套件在滿足所有約束條件下,實現整個設計只需占用 3/4 的器件資源。這意味著用戶可以為自己的設計添加更多的邏輯功能和片上存儲器,甚至可以采用更小型的器件。”

圖 2:Vivado 設計套件的多維分析算法可創建專門針對最佳時序、擁塞和走線長度(而不僅僅只是針對最佳時序)優化的布局。

功耗優化和分析

當今時代, 功耗是FPGA設計中最關鍵的環節之一。因此,Vivado設計套件的重點就是專注于利用先進的功耗優化技術,為用戶的設計提供更大的功耗降低優勢。“我們在技術上采用了目前在ASIC工具套件中可以見到的先進的時鐘門控制技術,通過該技術可以擁有設計邏輯分析的功能,同時消除不必要的翻轉”Feist表示 “具體來說,新的技術側重于翻轉因子 ‘alpha’,它能夠降低30%的動態功耗”Feist說,賽靈思去年在ISE設計套件中開始應用該技術, 并一直沿用至今。 Vivado將繼續加強這一技術的應用。

此外,有了這一新的可擴展的數據共享模型,用戶可以在設計流程的每一個階段得到功耗的估值,從而可以在問題發展的前期就能預先進行分析, 從而能夠在設計流程中,先行解決問題。

簡化工程變更單(ECO)

增量流量讓快速處理小的設計更改成為可能,每次更改后只需重新實現設計的一小部分,使迭代速度更快。它們還能在每個增量變化之后實現性能的表現,從而無需多個設計迭代。為此,Vivado設計套件還包括對一個流行的ISE FPGA編輯器工具的新的擴展,稱為Vivado器件編輯器。Feist說,在一個布局布線設計上使用Vivado器件編輯器,設計師現在有能力去做移動單元, 重新布線, 連接一個寄存器輸出作為調試管腳, 修改DCM或者查找表(LUT)的參數的工程變更單(ECO)——在設計周期的后期,無需通過返回設計重新綜合和實現。他說,目前行業沒有任何其他FPGA設計環境可以提供這種級別的靈活性。

基于業界標準而打造

四年半前, 當賽靈思開始從頭打造Vivado設計套件的時候,架構打造的首要任務,就是用標準的設計環境代替專有格式。致力于打造一個開放的環境,讓客戶能夠用 EDA 工具和第三方 IP 進行擴展。例如,Vivado 設計套件可支持 SDC(Synopsys 設計約束)、ARM AMBA AXI 4 IP互聯標準、IP-XACT IP封裝和交付標準,并且在新環境中提供了強大的互動 TCL 腳本功能。。

評論