針對未來十年 “All Programmable”器件的顛覆之作

可擴展的數據模型架構

本文引用地址:http://www.104case.com/article/131872.htm為減少迭代次數和總體設計時間,并提高整體生產力,賽靈思用一個單一的、共享的、可擴展的數據模型建立其設計實現流程,這種框架也常見于當今最先進的 ASIC 設計環境。Feist 說:“這種共享、可擴展的數據模型可讓流程中的綜合、仿真、布局規劃、布局布線等所有步驟在內存數據模型上運行,故在流程中的每一步都可以進行調試和分析,這樣用戶就可在設計流程中盡早掌握關鍵設計指標的情況,比如時序、功耗、資源利用和布線擁塞等。而且這些指標的估測將在實現過程中隨著設計流程的推進而更趨于精確。”

具體來說,這種統一的數據模型使賽靈思能夠將其新型多維分析布局布線引擎與套件的 RTL 綜合引擎、新型多語言仿真引擎以及 IP 集成器 (IP Integrator)、引腳編輯器 (Pin Editor)、布局規劃器 (Floor Planner)、芯片編輯器 (Chip Editor) 等功能緊密集成在一起。此外,該數據模型使賽靈思能夠為該工具套件配備全面的交叉探測功能,以便用戶跟蹤并交叉探測原理圖、時序報告、邏輯單元或其它視圖,直至 HDL 代碼中的給定問題。

Feist說:“用戶現在可以對設計流程中的每一步進行分析,而且環環相扣。在綜合后的流程中,我們還提供時序、功耗、噪聲和資源利用分析功能。所以如果很早就發現時序或功耗不符合要求,我可以通過短時迭代,前瞻性地解決問題,而不必等到布局布線完成后多次執行長時間迭代來解決。”

Feist 指出,這種可擴展數據模型提供的緊密集成功能還增強了按鍵式流程的效果,從而可滿足用戶對工具實現最大自動化,完成大部分工作的期望。Feist 表示,這種模型還能夠滿足客戶對更高級的控制、更深入的分析以及掌控每個設計步驟進程的需要。

芯片規劃層次化,快速綜合

Feist說, Vivado為用戶提供了設計分區的功能, 可以分別處理綜合、執行、驗證的設計, 使其可以在執行大型項目時,可以成立不同的團隊分頭設計。 同時,新的設計保存功能可以實現時序結果的復用, 并且可以實現設計的部分可重配置。

Vivado還包括一個全新的綜合引擎,旨在處理數以百萬計的邏輯單元。新的綜合引擎的關鍵是對System Verilog的強大支持。“Vivado的綜合引擎對System Veriog語言可綜合子集的支持, 比市場上任何其他工具都更好” Feist 說。 它的綜合速度是賽靈思ISE Design Suite綜合工具XST的三倍,并支持“快速”模式,使得設計師迅速把握設計的面積和規模。 另外,也讓他們調試問題的速度比之前采用RTL或門級原理圖快15倍。隨著越來越多的ASIC設計者轉向可編程平臺,賽靈思還在整個Vivado設計流程中提升了了Synopsys 設計約束 (SDC)。標準的使用開啟了一個新的自動化水平, 客戶現在可以訪問先進的EDA工具產生約束、檢查跨時鐘域、形式驗證, 甚至是利用像Synopsys PrimeTime那樣的工具進行靜態時序的分析。

多維度分析布局器

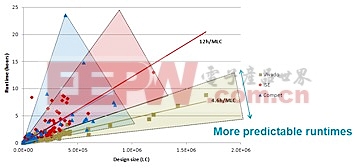

Feist 解釋說,上一代 FPGA 設計套件采用單維基于時序的布局布線引擎,通過模擬退火算法隨機確定工具應在什么地方布置邏輯單元。使用這類工具時,用戶先輸入時序,模擬退火算法根據時序先從隨機初始布局種子開始,然后在本地移動單元,“盡量”與時序要求吻合。Feist 說:“在當時這種方法是可行的,因為設計規模非常小,邏輯單元是造成延遲的主要原因。但今天隨著設計的日趨復雜化和芯片工藝的進步,互聯和設計擁塞一躍成為延遲的主因。采用模擬退火算法的布局布線引擎對低于 100 萬門的 FPGA 來說是完全可以勝任的,但對超過這個水平的設計,引擎便不堪重負。不僅僅有擁塞的原因,隨著設計的規模超過100萬門,設計的結果也開始變得更加不可預測。”

著眼于未來,賽靈思為 Vivado 設計套件開發了新型多維分析布局引擎,其可與當代價值百萬美元的 ASIC布局布線工具中所采用的引擎相媲美。該新型引擎通過分析可以找到從根本上能夠最小化設計三維(時序、擁塞和走線長度)的解決方案。Feist 表示:“Vivado設計套件的算法從全局進行優化,同時實現了最佳時序、擁塞和走線長度,它對整個設計進行通盤考慮,不像模擬退火算法只著眼于局部調整。這樣該工具能夠迅速、決定性地完成上千萬門的布局布線,同時保持始終如一的高結果質量(見圖 1)。由于它能夠同時處理三大要素,也意味著可以減少重復運行流程的次數。”

圖1:與其它 FPGA 工具相比,Vivado 設計套件能夠以更快的速度、更優異的質量完成各種規模的設計

評論