55nm創新工藝震動消費類終端ASIC設計服務市場

完整、經過驗證的IP加速上市時間

本文引用地址:http://www.104case.com/article/126217.htm富士通半導體的ASIC/COT業務部門是一個完全獨立的業務部門,一直給人非常低調的印象。多年來,他們通過整合自身在半導體工藝技術、關鍵IP和先進設計方法論上的巨大優勢,一直在為包含終端消費類應用的IC客戶和高速網絡通信類的IC客戶提供可靠而又完整的ASIC解決方案和增值的服務。

早在上世紀90年代,該公司就在中國大陸開始推廣ASIC方案和設計服務,最初客戶以通訊和網絡IC公司為主。2006年,該公司又在中國開始推廣其日本代工廠的COT服務,以便為中國客戶提供90nm和65nm工藝的ASIC設計、IP、晶圓代工等多元化的服務,很多應用如衛星電視、CMMB等消費類應用芯片都是在富士通日本晶圓廠投片生產的(40nm以下設計是轉由臺積電代工)。從2008年開始起, 他們中國客戶中消費類電子IC廠商的比重逐年升高。

“我們深諳中國市場的風格,所以在服務上保持著靈活的風格,確保客戶更以滿意的性價比實現先進的ASIC設計和制造。”劉琿說,“另外,從晶圓代工、IP授權、設計服務以及封裝測試,我們強調的是一站式增值設計服務,可將客戶的成本、風險、上市時間降至最低。”

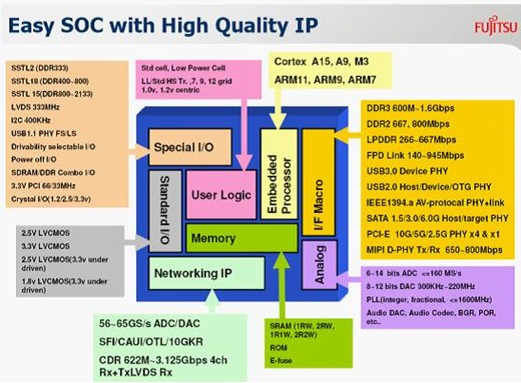

上市時間是消費類終端芯片產品取得成功的最重要因素,而迅速地整合IP資源是達到這一訴求的關鍵。富士通半導體提供非常完整的針對這類應用芯片的解決方案,提供諸如USB、HDMI、PCIE、SATA、MIPI、ARM CPU、AD/DA電源管理等諸多經過嚴格評估和量產驗證的IP。而這些IP大部分都是富士通內部開發的,如此省去了客戶為尋找各個IP而去和不同IP供應商談判的時間。從芯片的風險角度來講,一旦芯片出現IP的質量問題,客戶也無需為此而在各個IP供應商之間周旋。從成本角度,富士通半導體所提供的打包IP方案也會幫助節省客戶初期的IP 投入。

圖2:富士通半導體可提供完整、經過制造驗證的高品質IP。

上文提到的智能手機、平板電腦、智能電視等創新消費類終端應用需要有巨大的帶寬來支持,也就帶來通信網絡骨干網上傳輸設備技術的不斷革新的要求,從單模光纖傳輸10G到40G,再從40G到100G,未來還再向400G甚至一“太”比特的傳輸級別發展。

超高速模擬混合IP(55G-65G CMOS ADC/DAC IP)的面市使得承載更大通信帶寬的100G技術提前成為現實,助推整個產業革命。目前富士通是全球掌握此項技術領先的半導體廠商,通過整合富士通其他高速通信接口IP(Serdes)和全球化的設計資源,富士通半導體在光傳輸網領域成為全球最有競爭力的ASIC廠商之一。

據悉,目前已有多家世界頂級通信設備供應商使用了富士通的IP應用到100G網絡建構方案中,使得100G傳輸網在世界范圍內比預期提前2年實現商用。劉琿頗有感觸地說:“這也許不像Apple對我們生活的改變那么直觀,但是大家都知道,如今的世界就是一個構建在網絡上的世界,因此我可以自豪地說,富士通的ADC也是改變世界的幕后英雄!”

優勢的ASIC設計方法論(methodology)

本次富士通半導體推出的針對消費類終端的55nm創新工藝部分體現了富士通半導體在低功耗制程上所具備的優勢。對于通常都在上億門設計規模的100G網絡傳輸設備ASIC又該如何應對功耗方面的挑戰呢?

圖3:富士通半導體的動態電壓調整(DVS)設計技巧。

電機保護器相關文章:電機保護器原理

評論