芯片測(cè)試:系統(tǒng)級(jí)測(cè)試(SLT)詳解

在IC封測(cè)中我們常常會(huì)聽到:SLT、EVB、ATE這幾個(gè)名詞。它們之間的區(qū)別簡要如下:

?ATE(Auto Test Equipment) 在測(cè)試工廠完成. 大致是給芯片的輸入管道施加所需的激勵(lì)信號(hào),同時(shí)監(jiān)測(cè)芯片的輸出管腳,看其輸出信號(hào)是否是預(yù)期的值。有特定的測(cè)試平臺(tái)。?SLT(System Level Test) 也是在測(cè)試工廠完成,與ATE一起稱之為Final Test. SLT位于ATE后面,執(zhí)行系統(tǒng)軟件程序,測(cè)試芯片各個(gè)模塊的功能是否正常。?EVB(Evaluation Board) 開發(fā)板:軟件/驅(qū)動(dòng)開發(fā)人員使用EVB開發(fā)板驗(yàn)證芯片的正確性,進(jìn)行軟件應(yīng)用開發(fā)。

系統(tǒng)級(jí)測(cè)試(SLT)詳解前言最近去產(chǎn)線見識(shí)了一下機(jī)臺(tái),今天先一同來學(xué)習(xí)一下SLT。

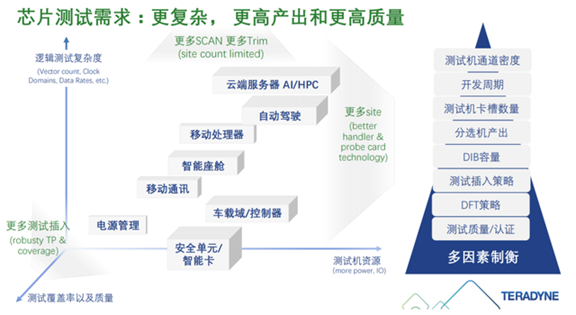

在半導(dǎo)體晶體管尺寸越來越小、芯片功能日益復(fù)雜的趨勢(shì)下,系統(tǒng)級(jí)測(cè)試(簡稱SLT)變得至關(guān)重要。那什么是SLT?

SLT是如何幫助提高產(chǎn)品質(zhì)量并縮短上市時(shí)間的?

什么是系統(tǒng)級(jí)測(cè)試?它有什么特別之處?系統(tǒng)級(jí)測(cè)試(SLT)是指在仿真的終端使用場景中對(duì)待測(cè)芯片(DUT)進(jìn)行測(cè)試,純粹通過運(yùn)行和使用來完成測(cè)試,無需像傳統(tǒng)自動(dòng)測(cè)試設(shè)備(ATE)那樣創(chuàng)建測(cè)試向量,但是仍需要編寫測(cè)試,只是編寫方式不同。測(cè)試流程如下:

?? 執(zhí)行特定操作。該操作可能是系統(tǒng)使用過程中固有的,如啟動(dòng)操作系統(tǒng);也可能是運(yùn)行某些功能模塊編寫的特定程序, 如性能評(píng)估程序。?? 判斷該操作是否成功,是依據(jù)測(cè)量的結(jié)果或該操作的成功/失敗來進(jìn)行衡量。例如,在驗(yàn)證某個(gè)內(nèi)部進(jìn)程是否成功執(zhí)行時(shí), 判斷的依據(jù)可以是操作系統(tǒng)是否成功啟動(dòng);或檢查某個(gè)測(cè)量值(性能測(cè)試結(jié)果與閥值的比較)

大多數(shù)情況下,SLT中的系統(tǒng)會(huì)配備一些板載處理器來執(zhí)行測(cè)試流程。由于片上系統(tǒng)(SoC)和系統(tǒng)級(jí)封裝(SIP)芯片是SLT的主要測(cè)試對(duì)象,因此測(cè)試用處理器通常就是待測(cè)芯片的一部分。如果不是此種情況,待測(cè)芯片的外圍測(cè)試系統(tǒng)通常會(huì)配備 一個(gè)合適的處理器。

SLT的測(cè)試時(shí)間比傳統(tǒng)ATE的測(cè)試時(shí)間長很多,因?yàn)镾LT是模擬真實(shí)終端使用場景的功能測(cè)試,而不是ATE中的結(jié)構(gòu)測(cè)試。SLT的測(cè)試時(shí)間一般都超過一分鐘,甚至可能長達(dá)數(shù)十分鐘,典型的測(cè)試時(shí)間為10分鐘左右。

由于測(cè)試時(shí)間較長,與傳統(tǒng)ATE測(cè)試相比,SLT測(cè)試設(shè)備必須具有更高的工位密度和更低的工位成本。

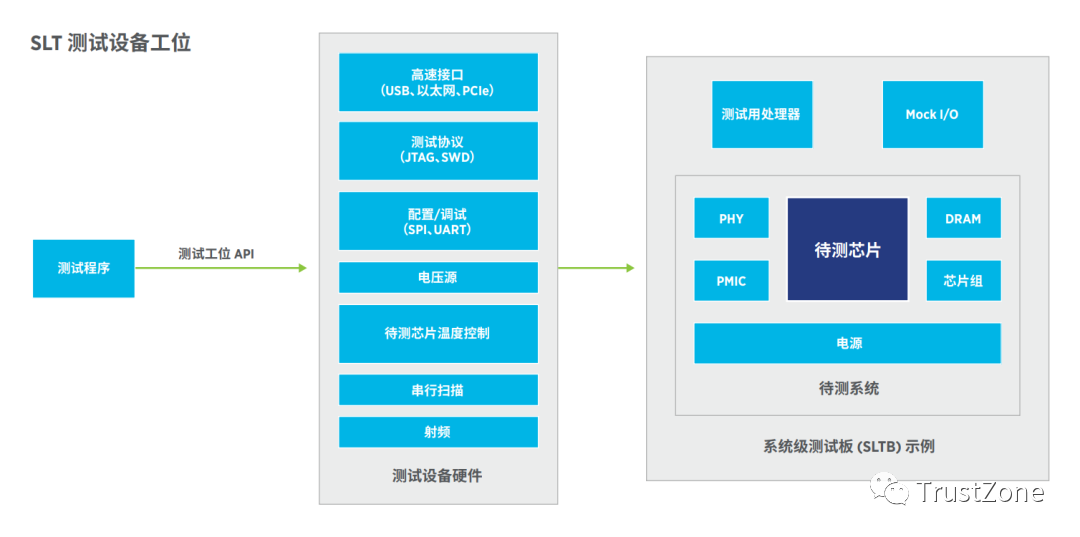

SLT概覽1. 系統(tǒng)在生產(chǎn)環(huán)境中執(zhí)行SLT需要構(gòu)建一個(gè)系統(tǒng)。SLT中的系統(tǒng)是在測(cè)試板上實(shí)現(xiàn)的,該測(cè)試板與最終使用該芯片的產(chǎn)品的電路板非常相似。測(cè)試板可能包括以下功能和特性:

?01、與待測(cè)芯片相匹配的引腳底座?02、可放在測(cè)試板上的所有待測(cè)芯片外設(shè),包括:?PMIC?RAM?存儲(chǔ)(如NVMe、eMMC)?SD卡?USB閃存?PCIe外設(shè)(如NVMe)?03、仿真電路和回環(huán),用于無法放在測(cè)試板上的外設(shè),例如人機(jī)接口設(shè)備(HID)和HDMI,在下圖中用Maock I/O模塊表示?04、測(cè)試用處理器(待測(cè)芯片不是測(cè)試用處理器的情況下)?05、測(cè)試設(shè)備和測(cè)試用處理器之間的通信方式?06、終端應(yīng)用中使用的系統(tǒng)軟件

系統(tǒng)級(jí)測(cè)試中非常關(guān)鍵的一點(diǎn)是,它將軟件看成是系統(tǒng)的一部分。這有助于:

?盡可能重現(xiàn)終端使用環(huán)境?測(cè)試硬件和軟件的交互方式

2. 測(cè)試機(jī)連接到測(cè)試板時(shí),測(cè)試設(shè)備至少需要提供以下功能和特性:

?測(cè)試板和待測(cè)芯片的電源?與測(cè)試用處理器交互的方式

更為先進(jìn)的SLT測(cè)試設(shè)備還具有以下功能和特性:

?01、連接到嵌入式處理器控制臺(tái)的UART接口,用于實(shí)現(xiàn)設(shè)備間的通信?02、JTAG,用于直接訪問待測(cè)芯片?03、串行外設(shè)接口SPI,用于訪問測(cè)試板上的功能?04、高速串行接口,如PCIe、以太網(wǎng)或USB?05、自動(dòng)溫度控制?06、具有相當(dāng)?shù)目臻g以容納客戶設(shè)計(jì)的測(cè)試板卡及模塊?07、測(cè)試板上閃存設(shè)備的自動(dòng)更新

除了具備以上所說的硬件功能以外,測(cè)試設(shè)備還必須提供一個(gè)計(jì)算機(jī)平臺(tái)(測(cè)試用PC)和相應(yīng)的API,以便測(cè)試程序訪問這些功能和特性。

3. 測(cè)試創(chuàng)建SLT測(cè)試有多種不同的方法,所選的SLT測(cè)試設(shè)備應(yīng)該能夠靈活適應(yīng)不同方法。以下示例就展示了這種靈活性。

測(cè)試程序是多個(gè)單獨(dú)測(cè)試組成的集合或序列,通常在作為測(cè)試設(shè)備一部分的測(cè)試用PC上運(yùn)行。各個(gè)單獨(dú)的測(cè)試通常實(shí)現(xiàn)為代碼,在以下位置運(yùn)行:

?01、測(cè)試用PC?02、測(cè)試用處理器,可能是測(cè)試設(shè)備或測(cè)試板的一部分?03、處理器,待測(cè)芯片的一部分

在所有三種情況下,測(cè)試都可通過測(cè)試設(shè)備API或測(cè)試板上實(shí)現(xiàn)的接口來操作測(cè)試板和待測(cè)芯片。在最后一種情況下,測(cè)試可在待測(cè)芯片中運(yùn)行。

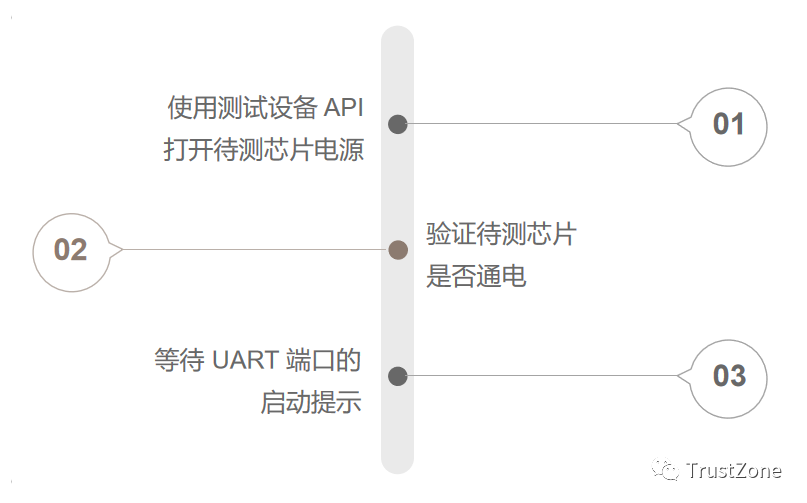

1)在測(cè)試用PC或測(cè)試用處理器上執(zhí)行測(cè)試 執(zhí)行測(cè)試用PC或測(cè)試用處理器上的測(cè)試的流程如下。在此示例中,測(cè)試旨在驗(yàn)證嵌入式處理器是否啟動(dòng)。假設(shè)待測(cè)芯片有 一個(gè)連接到測(cè)試設(shè)備UART控制臺(tái)的UART端口,則此測(cè)試最簡單的形式是:

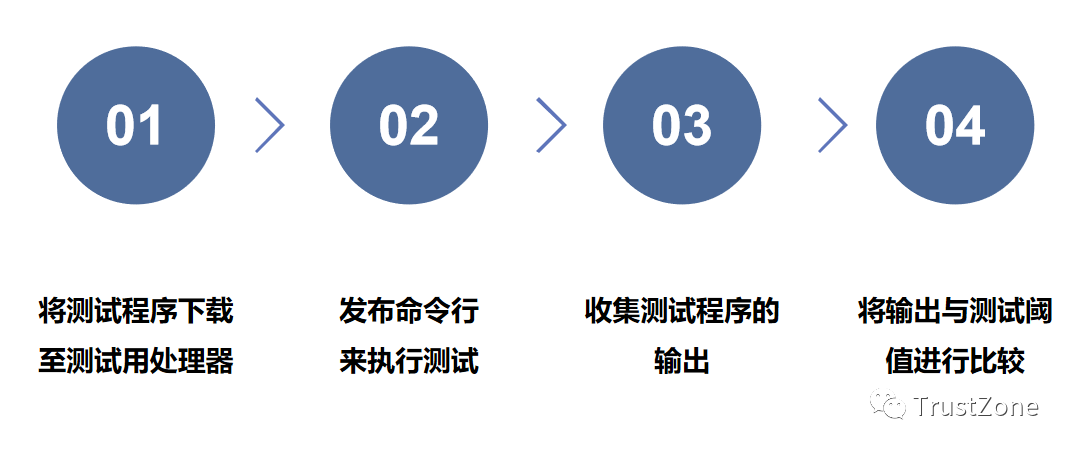

?2)在具有測(cè)試用處理器的待測(cè)芯片中執(zhí)行從測(cè)試用PC部署的測(cè)試 另一種類型的測(cè)試是從測(cè)試用PC部署到待測(cè)芯片本身的測(cè)試用處理器。在這種情況下,假設(shè)待測(cè)芯片有某種高速接口,可以通過該接口下載和執(zhí)行測(cè)試程序。這種測(cè)試的通用形式一般是:

?3)執(zhí)行直接存儲(chǔ)在測(cè)試板上的測(cè)試 另一種測(cè)試方式是將測(cè)試序列存儲(chǔ)在測(cè)試板上的非易失性存儲(chǔ)器中,從而節(jié)省下載時(shí)間。采用將測(cè)試下載至測(cè)試板的方式時(shí), 更容易更改測(cè)試。

當(dāng)然,在真實(shí)環(huán)境中,測(cè)試會(huì)更加復(fù)雜,需要驗(yàn)證許多事件。借助SLT測(cè)試設(shè)備的靈活性和測(cè)試板上待測(cè)芯片周圍的真實(shí)硬件,能夠更輕松地創(chuàng)建非常復(fù)雜的場景,這點(diǎn)對(duì)于傳統(tǒng)ATE來說很難或者根本無法實(shí)現(xiàn)。

4.SLT有什么獨(dú)特之處和優(yōu)勢(shì)系統(tǒng)級(jí)測(cè)試也被稱為功能測(cè)試。有段時(shí)間,大多數(shù)測(cè)試都是功能測(cè)試,但后來證明由于結(jié)構(gòu)測(cè)試能夠自動(dòng)化,可以更有效地 滿足故障覆蓋率要求。因此,自動(dòng)測(cè)試程序生成(ATPG)成為測(cè)試向量的主要來源。

ATPG等結(jié)構(gòu)技術(shù)需要掃描鏈等人工結(jié)構(gòu),以便訪問整個(gè)電路,這使得大多數(shù)測(cè)試都是在測(cè)試模式下完成。雖然這對(duì)測(cè)試大有裨益,但可測(cè)試性設(shè)計(jì)(DFT)和ATPG也有缺點(diǎn),包括:

?01、測(cè)試模式掩蓋了僅在功能模式下可見的故障?02、ATPG 測(cè)試向量不會(huì)覆蓋電路所有部分,如IP塊之間的接口?03、待測(cè)芯片在結(jié)構(gòu)測(cè)試期間不會(huì)經(jīng)歷真實(shí)運(yùn)行,無法發(fā)現(xiàn)一些邊緣故障和滯后性的故障,包括以下差異:?電源和時(shí)鐘分配電路中的噪聲?測(cè)試向量導(dǎo)致待測(cè)芯片發(fā)熱?04、ATPG沒有覆蓋復(fù)雜的真實(shí)場景,手動(dòng)編寫這樣的測(cè)試向量可能非常困難甚至不可能?05、測(cè)試中不包括系統(tǒng)軟件

相較而言,使用SLT時(shí),測(cè)試工程師可以像在真實(shí)環(huán)境中一樣使用待測(cè)芯片,從而發(fā)現(xiàn)以前無法發(fā)現(xiàn)的故障。下期我們將探討SLT逐漸普遍的原因、SLT的實(shí)踐應(yīng)用、SLT面臨的挑戰(zhàn)。

5.SLT為什么越來越普遍?質(zhì)量要求日益提高過去十年里,我們生活的世界變得更加依賴電子設(shè)備。這點(diǎn)在汽車中尤為明顯:半自動(dòng)駕駛汽車已經(jīng)推出,電子設(shè)備或軟件能夠感知事件并通過自動(dòng)轉(zhuǎn)向或制動(dòng)來對(duì)事件做出反應(yīng)。

世界各地的人也都高度依賴手機(jī),而這需要強(qiáng)大可靠的設(shè)備作為基礎(chǔ)。對(duì)設(shè)備質(zhì)量的高要求推動(dòng)制造商對(duì)其芯片和系統(tǒng)進(jìn)行全面測(cè)試,以減少終端用戶購買后遇到問題的可能性。

不斷推向技術(shù)極限在當(dāng)今競爭激烈的市場中,元器件供應(yīng)商不斷推向技術(shù)極限,以提高性能、電池續(xù)航和良率。這意味著,供應(yīng)商需要:

?盡早在新的工藝節(jié)點(diǎn)上發(fā)貨,而工藝的缺陷率可能仍然比較高?盡可能以低電壓運(yùn)行,以延長電池續(xù)航?微調(diào)PLL設(shè)置以最大化良率?轉(zhuǎn)為使用更前沿的封裝技術(shù)來提高密度和性能

鑒于上述需求,必須進(jìn)行大量測(cè)試,確保成品中使用的是優(yōu)質(zhì)元器件。因此,隨著不斷推向技術(shù)極限,使用SLT可防止故障漏檢,確保成品元器件達(dá)到所需的高質(zhì)量水準(zhǔn)。

測(cè)試覆蓋率仍有待提高鑒于進(jìn)入測(cè)試時(shí)的初始缺陷率升高,而退出測(cè)試時(shí)允許的缺陷率顯著降低,元器件制造商比以往任何時(shí)候都更加依賴測(cè)試。

目前的技術(shù)已經(jīng)遠(yuǎn)遠(yuǎn)超過每個(gè)芯片10億個(gè)晶體管的大關(guān),99.5%的故障覆蓋率雖然仍可以接受,但如果以10億件來計(jì)算,0.5%還是很多。

電子設(shè)計(jì)自動(dòng)化(EDA)行業(yè)在實(shí)現(xiàn)故障覆蓋率與密度同步提高方面付出了巨大努力,但由于以下原因,故障覆蓋率的提升有所滯后。

故障模式每當(dāng)在集成電路制造中引入新的創(chuàng)新技術(shù),也意味著引入了新的故障模式。但檢測(cè)這些故障模式所需的新測(cè)試技術(shù)卻開發(fā)緩慢,總是難以跟上步伐。而通過SLT,制造商可以實(shí)施功能測(cè)試,以引發(fā)和捕獲由新故障模式導(dǎo)致的真實(shí)故障。

除了具備以上所說的硬件功能以外,測(cè)試設(shè)備還必須提供一個(gè)計(jì)算機(jī)平臺(tái)(測(cè)試用PC)和相應(yīng)的API,以便測(cè)試程序訪問這些功能和特性。

SoC內(nèi)部接口ATPG專注于測(cè)試IP塊并為這些IP塊實(shí)現(xiàn)非常高的故障覆蓋率。然而,隨著SoC變得越來越復(fù)雜,加入更多IP塊,這些IP塊之間的接口成為芯片中更重要的組成部分,導(dǎo)致整體故障覆蓋率下降。

IP塊接口的另一個(gè)挑戰(zhàn)是它們通常是異步的,這就導(dǎo)致測(cè)試更加困難。除了測(cè)試異步接口的復(fù)雜度,掃描所有可能的時(shí)序組合也非常耗時(shí)。

EDA行業(yè)提供了推動(dòng)SoC系統(tǒng)驗(yàn)證的工具,但尚不清楚這些仿真將如何移植到ATE,甚至能否移植到ATE。

SLT支持對(duì)接口進(jìn)行測(cè)試,因?yàn)榇郎y(cè)芯片將在真實(shí)環(huán)境中使用,以便發(fā)現(xiàn)ATE中可能沒有出現(xiàn)的故障。

通過SLT進(jìn)行設(shè)計(jì)驗(yàn)證如今的系統(tǒng)非常復(fù)雜,因此缺陷很難避免。設(shè)計(jì)驗(yàn)證環(huán)節(jié)應(yīng)該在零件或系統(tǒng)投入生產(chǎn)之前發(fā)現(xiàn)這些缺陷,但是,其中一些設(shè)計(jì)缺陷很難察覺,這就導(dǎo)致許多系統(tǒng)需要運(yùn)行很長時(shí)間才能出現(xiàn)這種系統(tǒng)故障形式的缺陷。

更多時(shí)候,發(fā)現(xiàn)這些缺陷所需的硬件實(shí)例數(shù)量大得不切實(shí)際。

作為替代方案,在預(yù)生產(chǎn)和早期生產(chǎn)中運(yùn)行SLT可以提供引發(fā)這些罕見故障所需的大量待測(cè)芯片,以便在產(chǎn)品交付給終端客戶之前修復(fù)硬件或軟件中的缺陷。

邊緣故障通常是裕度設(shè)計(jì)不佳造成的結(jié)果,因此SLT發(fā)現(xiàn)邊緣故障的能力有助于在流程早期階段解決這些裕度設(shè)計(jì)問題。

裕度設(shè)計(jì)是指為了保證結(jié)構(gòu)的安全可靠性,在設(shè)計(jì)中引入一個(gè)大于1的安全系數(shù),試圖來保障機(jī)械零件不發(fā)生故障。安全系數(shù)是通過綜合考慮荷載、材料性能數(shù)據(jù)的可靠性、所計(jì)算方法的合理性、加工裝配精度以及所設(shè)計(jì)的零件的重要性、失效后果等因素來確定。

在裕度設(shè)計(jì)中,對(duì)于配合尺寸和非配合尺寸,安全裕度的數(shù)值有所不同。一般而言,對(duì)于配合尺寸,安全裕度A的數(shù)值取工件公差的1/10;對(duì)于非配合尺寸或工藝能力很高時(shí),A值可取為零。同時(shí),A值的大小是人為給定的,A值越大對(duì)計(jì)量器具要求越低;A值越小,生產(chǎn)公差越大,但對(duì)計(jì)量器具的要求越高。因此應(yīng)結(jié)合實(shí)際情況靈活處理。

6.SLT的實(shí)踐應(yīng)用裕度設(shè)計(jì)通常也稱為安全系數(shù)法,是一種廣泛用于機(jī)械可靠性設(shè)計(jì)領(lǐng)域的設(shè)計(jì)方法。

用SLT有多種不同策略。之前提到了SLT能夠提高復(fù)雜待測(cè)芯片的故障覆蓋率,此外還有其他優(yōu)勢(shì),包括:

?為制造和測(cè)試提供早期反饋。此類反饋用于減少缺陷和提高故障覆蓋率。?快速提高故障覆蓋率以避免漏檢。?實(shí)現(xiàn)難以在ATE上實(shí)現(xiàn)的測(cè)試。

完整SLT與局部SLT對(duì)比 本白皮書主要介紹使用完整SLT以實(shí)現(xiàn)更高質(zhì)量,但也存在其他使用可能性:

?1) SLT抽樣測(cè)試 對(duì)于過往記錄良好、基于成熟工藝、在ATE上具有良好故障覆蓋率的待測(cè)芯片,SLT可能并不是必需的。但是,使用SLT對(duì)部件進(jìn)行抽樣測(cè)試有利于驗(yàn)證是否達(dá)到每百萬缺陷數(shù)(DPPM)要求。?2) 初始斜波期間或降低缺陷率時(shí)使用完整SLT?用于發(fā)現(xiàn)ATE未檢出的故障,找出SLT所發(fā)現(xiàn)故障的根本原因*,然后創(chuàng)建ATE測(cè)試進(jìn)行驗(yàn)證。同時(shí),來自SLT的反饋可用于降低工藝的缺陷率。如此一來,測(cè)試覆蓋率和缺陷率都有了改進(jìn),最后只需抽樣檢查即可。?3) 全面生產(chǎn)SLT 當(dāng)使用傳統(tǒng)ATE無法實(shí)現(xiàn)必要的覆蓋率,或由于高工藝缺陷率而導(dǎo)致漏檢率過高時(shí),可使用此方法。?4) 快速提高故障覆蓋率以避免漏檢 理想情況下,遇到系統(tǒng)故障時(shí),應(yīng)找出故障的根本原因,修復(fù)故障并添加測(cè)試來捕獲其他故障,但這個(gè)過程需要時(shí)間,而更理想的方法是立即停止漏檢。SLT非常適合這一用途,它可以用來捕獲ATE的漏檢故障,然后可以將測(cè)試快速添加到SLT,以檢測(cè)出影響終端用戶的漏檢。SLT提供的測(cè)試方法,對(duì)于標(biāo)準(zhǔn)ATE來說非常困難甚至不可能,因此,對(duì)于某些現(xiàn)場故障,SLT是少數(shù)幾種達(dá)到故障覆蓋率要求的方法之一。

SLT面臨的挑戰(zhàn)難以量化故障覆蓋率由于沒有可用的工具能夠衡量SLT對(duì)傳統(tǒng)故障模式的故障覆蓋率,因此很難知道所作的測(cè)試是否足夠。

有一些手動(dòng)方法可幫助了解SLT測(cè)試的全面性,包括根據(jù)定義系統(tǒng)場景、列出所有要測(cè)試的場景,然后驗(yàn)證針對(duì)這些場景的測(cè)試是否足夠。

EDA供應(yīng)商已經(jīng)開始為基于場景的SLT生產(chǎn)合適的工具。

無法測(cè)量裕度傳統(tǒng)ATE測(cè)試設(shè)備具有高精度板卡,可以測(cè)量部件的規(guī)格,例如邊緣器件排布、電壓、電流、頻率和DAC/ADC線性度。

SLT則有所不同:功能測(cè)試可以告訴我們給定的待測(cè)芯片是否正常工作,但它不能告訴我們待測(cè)芯片是處于故障邊緣,還是有充足的裕度,可以繼續(xù)正常工作。

測(cè)試板的差異性與裕度問題相關(guān)的是,用于構(gòu)建測(cè)試板的元器件本身具有不同程度的裕度,這意味著待測(cè)芯片的測(cè)試結(jié)果可能取決于所采用的測(cè)試板的規(guī)格。

如果大量測(cè)試板不符合規(guī)范,并且是由于測(cè)試板設(shè)計(jì)缺陷而導(dǎo)致待測(cè)芯片失敗,這將是一場災(zāi)難。但是,如果測(cè)試板都符合規(guī)范,那么測(cè)試板的差異性反而有利于測(cè)試,因?yàn)檫@意味著待測(cè)芯片的測(cè)試更接近真實(shí)場景。

結(jié)語SoC和SIP的復(fù)雜度日益提高,加上終端用戶日益嚴(yán)格的質(zhì)量要求,在此趨勢(shì)的推動(dòng)下,SLT得到了更廣泛的采用,成為待測(cè)芯片測(cè)試策略中的關(guān)鍵組成部分。

通過使用SLT在仿真的終端環(huán)境中對(duì)待測(cè)芯片進(jìn)行功能測(cè)試,設(shè)備制造商可以預(yù)防使用傳統(tǒng)晶圓和封裝測(cè)試技術(shù)難以檢測(cè)到的漏檢故障。

此外,在測(cè)試流程中添加SLT環(huán)節(jié)后,不僅可以捕獲漏檢故障,而且可以在平臺(tái)之間移動(dòng)測(cè)試,包括在測(cè)試流程的早期階段運(yùn)行低良率測(cè)試,后期階段在SLT測(cè)試設(shè)備中運(yùn)行高良率測(cè)試,這將有助于客戶達(dá)到理想的測(cè)試成本/質(zhì)量比。

我們看到,市場對(duì)SLT的需求不斷增長,并且很多企業(yè)都希望通過實(shí)現(xiàn)SLT來改進(jìn)質(zhì)量成本。

來源:內(nèi)存市場*博客內(nèi)容為網(wǎng)友個(gè)人發(fā)布,僅代表博主個(gè)人觀點(diǎn),如有侵權(quán)請(qǐng)聯(lián)系工作人員刪除。