繞過先進制程封鎖線,SDSoW技術深度揭秘。作者 | ZeR0

編輯 | 漠影

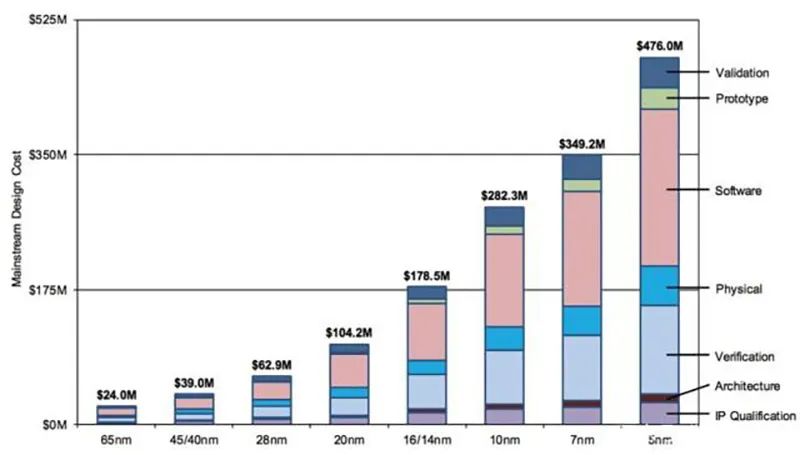

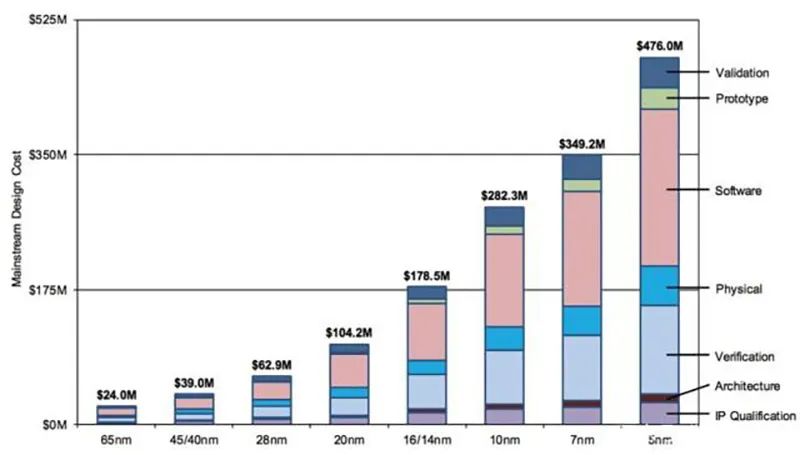

跨越先進芯片制程的屏障,已然迫在眉睫。看向全球,半導體產業景氣度持續低迷,多家巨頭半只腳已邁入寒冬。就連最新財季凈利飆漲的全球晶圓代工龍頭臺積電,也開始使出預警業績下滑、削減投資預算、關閉4臺EUV光刻機、鼓勵員工休假的“過冬”連環計。更大的糟心事還在接踵而至。10月蘋果、高通、英偉達、聯發科、AMD等臺積電大客戶的“砍單”余震還沒消止,尚未出世的臺積電3nm又被曝遭蘋果臨時“撤單”的暴擊,據傳臺積電已揮刀斬向自家供應鏈,砍單幅度高達40%~50%。作為全球先進制程爭霸賽中的“頭號贏家”,臺積電前不久還硬氣地向蘋果提出漲價,怎么這會兒又頹勢盡露?市場原因是,此前全球信息產業因經歷“缺芯”危機而大舉搶芯囤芯,提前預定各大晶圓廠不少產能。今年消費電子需求轉冷、設備商賣貨不暢,唇亡則齒寒,“砍單效應”層層傳遞至芯片業。技術原因是,臺積電首批3nm的表現“撲街”了。蘋果本就對供應鏈要求嚴苛且精打細算,結果臺積電3nm非但性能參數不達標、良品率低,成本還很高,對蘋果來說已經不是一筆劃算的買賣。但這也怪不得臺積電,3nm技術之困,其實是當前全球芯片產業都在面臨的殘酷境地——隨著硅基材料工藝逼近物理極限,技術演進越來越難,僅靠制程工藝的進步,已經帶不動芯片性價比的提升了。

▲芯片流片成本隨著制程工藝演進而迅速上升

不再奉摩爾定律為圭臬的半導體企業們,急需探出一條新路,以跟上旺盛暴漲的算力需求。這也是為什么近年來圍繞半導體材料、結構、封裝、工具等創新技術路徑紛紛走上快車道。對于中國大陸半導體產業而言,壓力更甚一籌。美國政府變本加厲地濫用國家力量,遏制阻滯中國大陸芯片產業的發展。在先進制造相關技術屢遭鉗制的背景之下,立足國情揚長避短,整合既有本土優勢,探索創新路徑,已是燃眉之急。在中國工程院院士鄔江興看來,比起削足適履,做一雙合腳的鞋,才是中國半導體產業的換道超車的機會所在。而能夠繞開先進制程屏障、將系統綜合效益顯著提升的SDSoW(軟件定義晶上系統)技術,也許就是雙合腳的鞋。

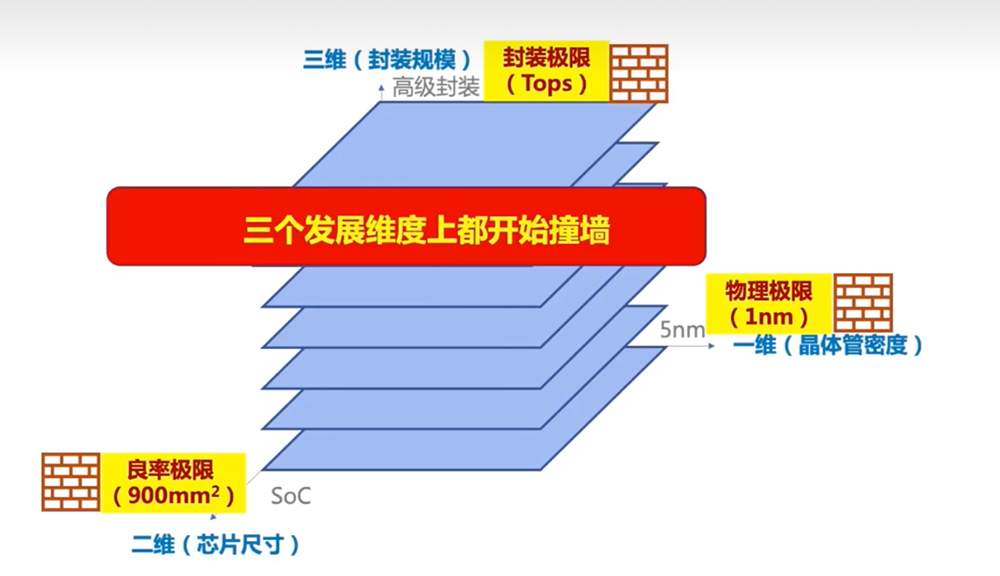

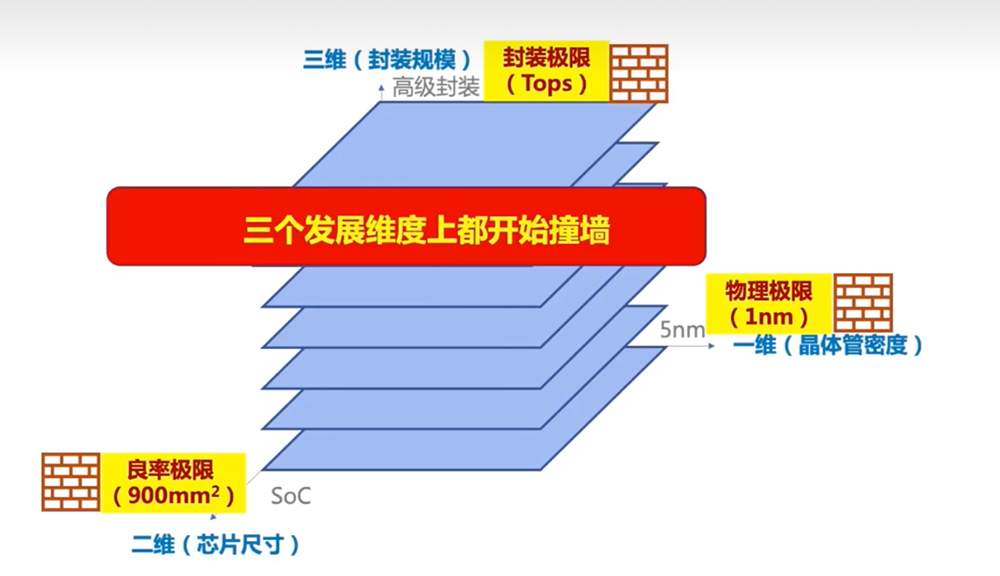

01.芯片發展面臨“三堵墻”計算架構變革時不我待

在信息化進程下,海量數據爆炸式增長,造成前所未有的數據挑戰:算不及、存不下、運不走。鄔江興院士曾總結當前芯片產業發展面臨的“三堵墻”。第一堵墻是物理極限,工藝節點進步逐漸逼近1nm物理極限;第二堵墻是良率極限,單芯片尺寸越做越大,但良率控制越來越難,合格率顯著下滑;第三堵墻是封裝極限,先進封裝技術遭遇散熱或規模瓶頸,功耗問題日益凸顯,難以支持大規模Die的高級封裝。

一方面,登納德縮放定律失效,摩爾定律放緩,令制程工藝進步對單芯片計算性能的貢獻比例不再顯著;另一方面,從芯片、模組、機匣、機架到系統,逐層堆疊的工程技術路線面臨性能、功耗、時延、可靠性等多方面的發展瓶頸。我們做個簡單推演:芯粒從晶圓被切出來,被封裝到模組,多個模組拼成板卡,多個板卡組成機架,眾多機架再組成分散到不同機房的集群,隨著通信范圍擴大,連接越來越稀疏,每過一級傳輸都會對帶寬施加限制,有效的算力、存儲力、網絡通信力層層折損,能效越來越低。也就是說,原本芯片能發揮出十成的功力,按照現有的“堆砌式”工程技術路線去走,等到系統層面,它的功力已經折損到只剩下一成。這就好比建設現代摩天大樓,如果用一塊磚頭一抹水泥的老辦法來堆砌,這棟樓越往上蓋承重壓力越大,而且根本扛不住地震暴風;要讓大樓足夠堅固穩定,必須根據超高層建筑結構的受力特點,來設計作為大樓中心支撐的整體鋼架。同樣,大型信息基礎設施亦是一個復雜精密的系統級工程,要減少從芯片到系統的“逐級插損”,需從計算體系結構層面進行全維創新。針對這些問題,鄔江興院士帶領團隊提出了軟件定義晶上系統(SDSoW,Software Defined System on Wafer),將大型信息基礎設施的工程技術路線從“逐層堆疊式”演進為由異質材料、不同制程工藝的各種芯粒異構集成的“拼接組裝式”。打個比方,“逐層堆疊式”路線像從鄉、縣到市再到省,一級一級地管理指揮;而“拼接組裝式”路線通過將所有芯粒集中放在一塊大晶圓上,實現了無插損的扁平化指揮。

據鄔江興院士團隊與寒武紀聯合測算,基于SDSoW技術路線,在28nm工藝條件下,僅用16塊晶圓,就能構建與美國超算Summit同等的算力,同時功耗僅為其1/80、占地面積為其1/16,造價僅為1/5;84塊晶圓即可構建E級機器,功耗僅有“堆砌式”系統的1/15、占地面積為其1/18、造價僅為其1/3。這樣對比來看,SDSoW能夠將整個大型信息基礎設施的綜合效益顯著提升,對于短期內破解“卡脖子”難題、中長期提供換道超車新路徑具有雙重戰略意義。即便先進工藝及工具受阻,SDSoW也能基于自主可控的國產技術及裝備資源,達到領先的系統性能水平。

這一技術路線究竟是怎么實現的?最新技術與生態進展如何?如何助力解決國產芯片自主化的痛點?近日,芯東西與鄔江興院士團隊核心成員進行深入交流。

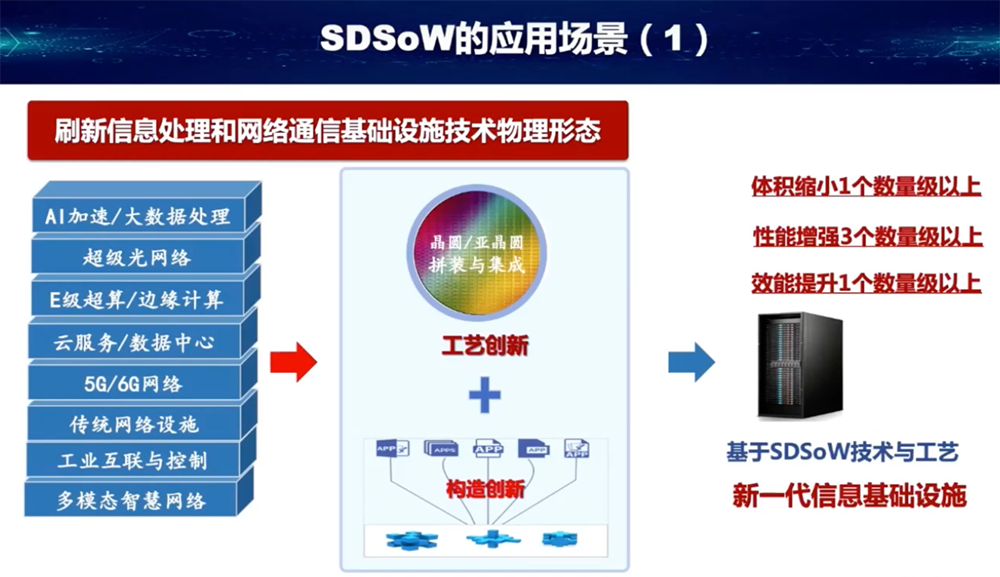

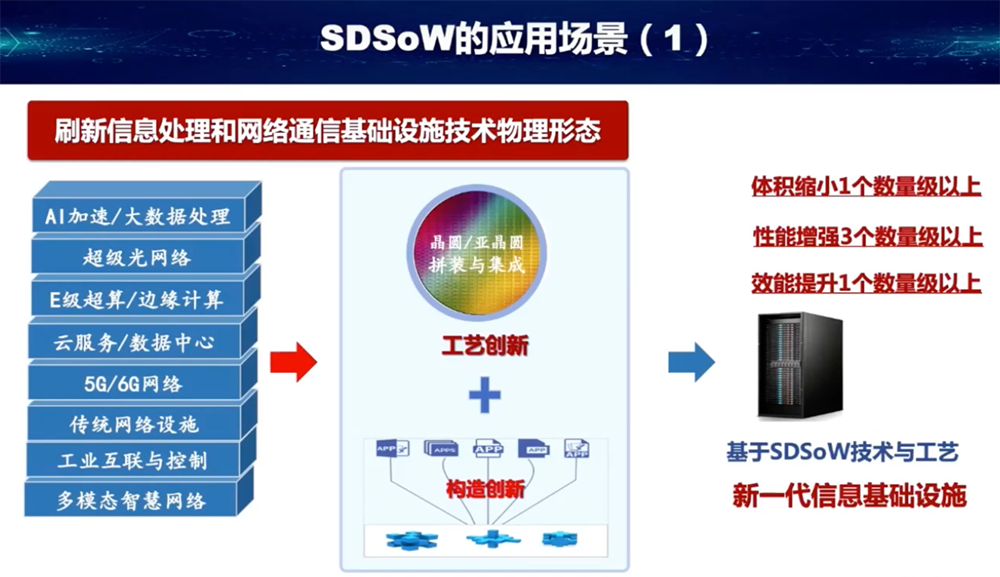

02.結構創新×工藝創新將異構異質芯粒靈活集成

SDSoW既可應用到數據中心、高性能計算、智能計算、算力網絡等涉及國計民生的大型信息基礎設施,又適用于需執行復雜功能的無人設備,如物聯網、網絡通信、無人機等。根據鄔江興院士在2020年6月舉行的第四屆未來網絡發展大會上做的演算:在相同工藝條件下,SDSoW有望在帶寬、延遲、能效、體積等方面帶來4~6個數量級以上的綜合增益。

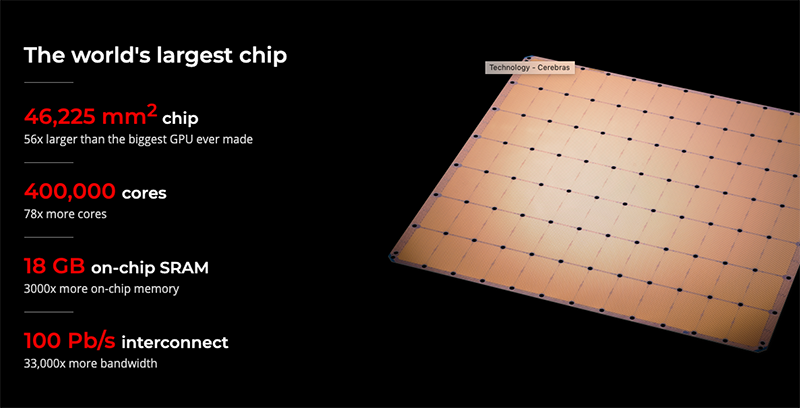

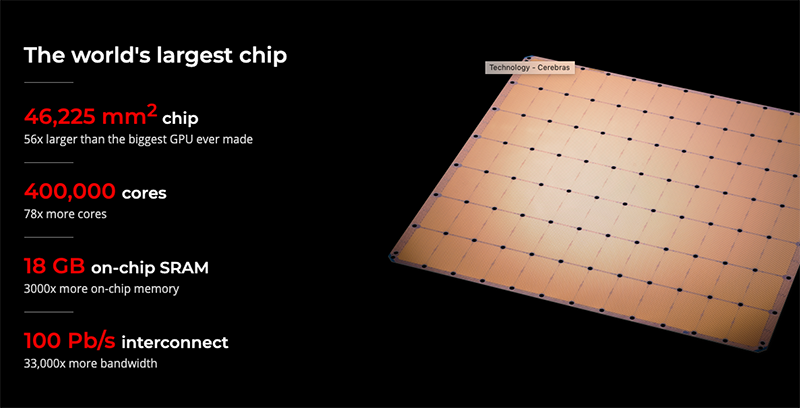

4~6個數量級,來自兩大關鍵組成“SD(軟件定義)”和“SoW(晶上系統)”的連乘性增益——軟件定義結構能帶來大概1~3個數量級的體系結構增益;晶圓級芯粒互連拼裝可將能耗、延遲降為原來的1/10甚至更少,將帶寬增加超10倍。關注芯片設計創新風向的讀者,想必會對2019年9月美國AI芯片創企Cerebras Systems推出的世界最大芯片“晶圓級引擎(WSE)”印象深刻。在整塊晶圓上集成了40萬個AI核心的WSE,便是一個基于晶圓級異構集成技術的SoW典例,最新推出的第二代,單顆晶圓級芯片則集成了85萬個AI核心!

▲晶圓級引擎WSE

WSE屬于同質同構集成,另一個異構集成的SoW典例是美國DARPA在電子復興(ERI)計劃中啟動的“通用異構集成和IP重用策略(CHIPS)”項目。該項目通過采用先進封裝技術,可將多個不同工藝的Chiplet集成在一起。但在鄔江興院士團隊核心成員看來,Chiplet也許能救某些產業或公司,但不能救中國。近年來SoW發展突飛猛進,成熟性、經濟性、規模性均得到驗證,然而目前仍是“戴著鐐銬跳舞”,現有相關研究通常基于剛性固定的體系結構,系統內部的計算、存儲、IO等資源都是固定的,各資源之間的連接關系和通信帶寬也相對固定。而在實際場景中,不同應用對計算、存儲、通信資源的要求各不相同,固化的系統結構在適配不同應用時會存在靈活擴展方面的局限性。SDSoW相比于SoW的一大差別,便在于此。

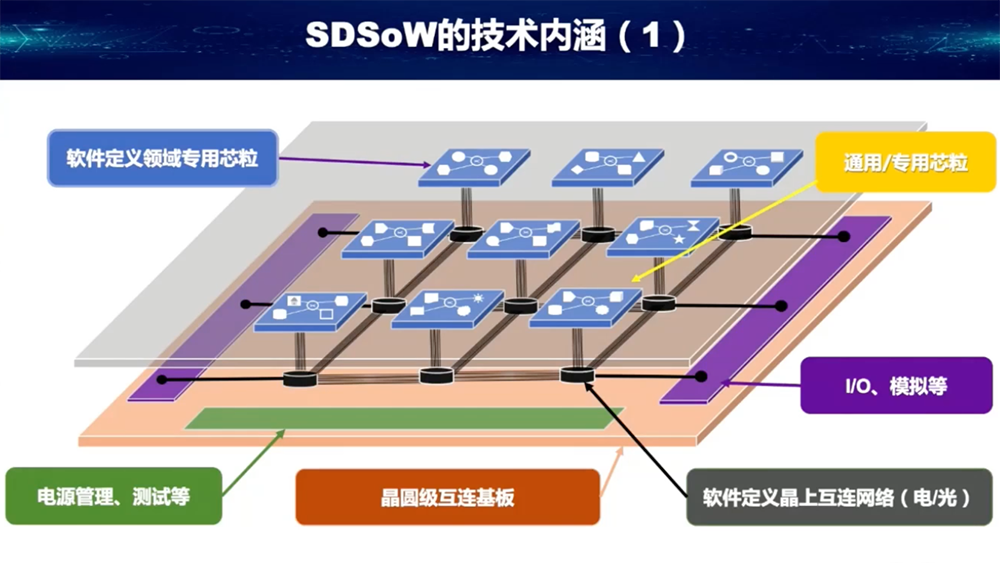

在SoW的基礎上,SDSoW在芯粒結構、系統、應用3個層面引入“軟件定義”,讓原本只能賦能一類應用的晶上系統,可利用軟件定義硬件滿足復雜多樣的應用任務需求,將晶上系統豐富的邏輯、存儲、網絡資源之性能與效能更大程度地釋放出來。“SoW是個三維空間,是個樓群,SD給這個樓群賦予了時間維度的屬性,使這個樓群向外展示的服務特性是隨時間變化的。”鄔江興院士團隊的核心成員解釋道,“簡單來說,就是一句話,有ASIC級的性能,有FPGA級的靈活性。”集成了成千上萬個芯粒的晶上系統,可以理解成小型云計算規模的計算、存儲和網絡資源,軟件定義則能夠讓SoW上的所有資源去適應結構,不僅具有云計算服務的集約化效益,而且還有大規模資源靈活變結構的效能增益。

03.軟件定義多層優化SDSoW計算結構詳解

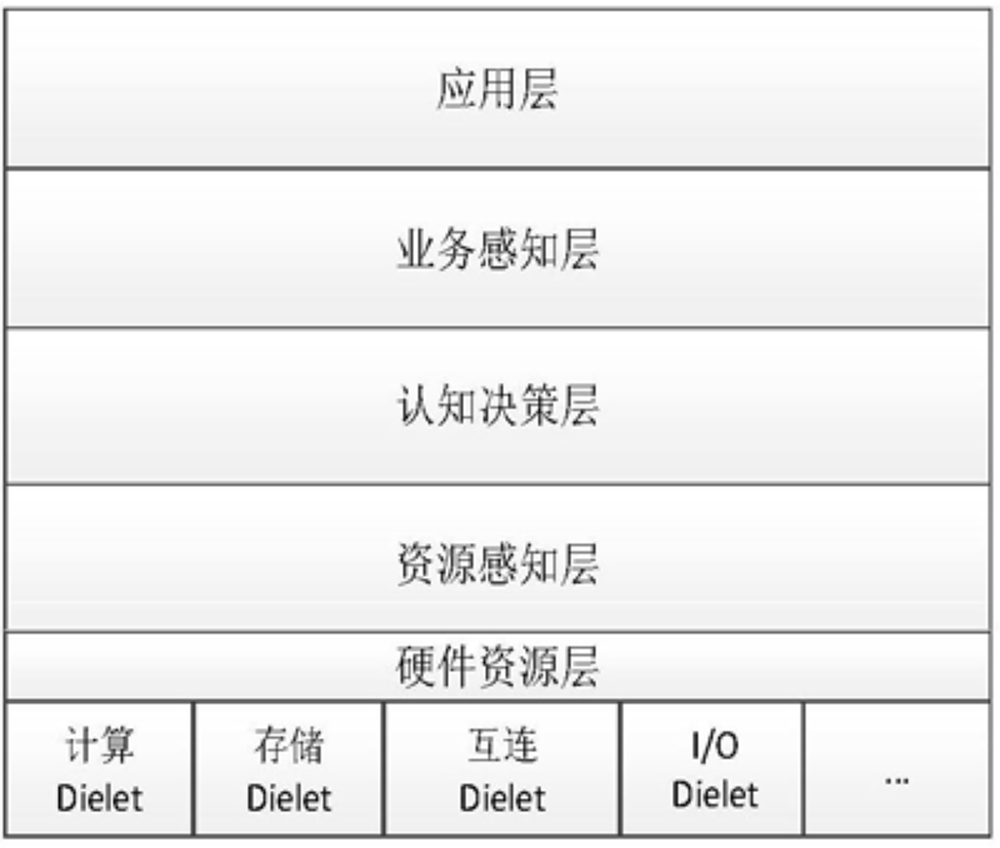

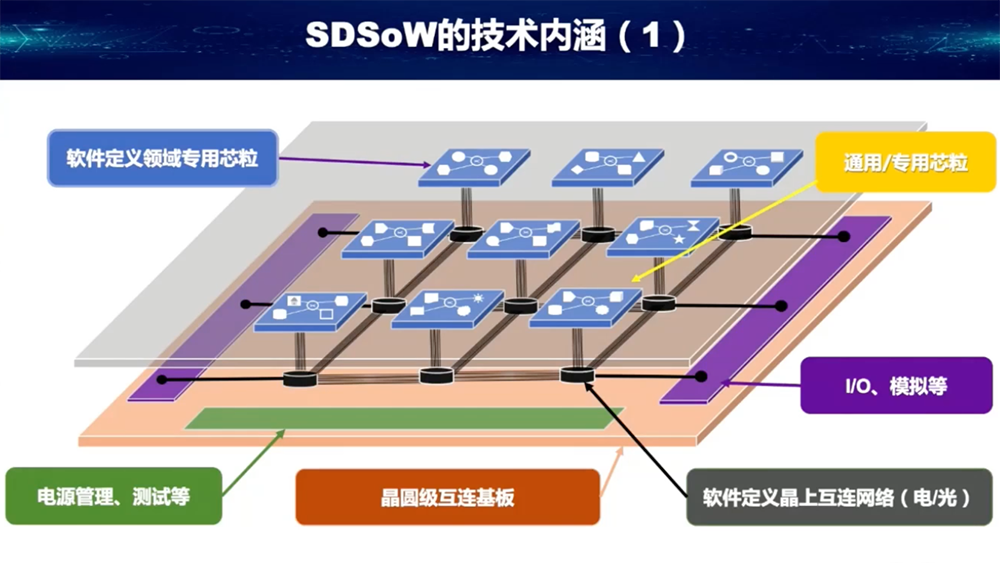

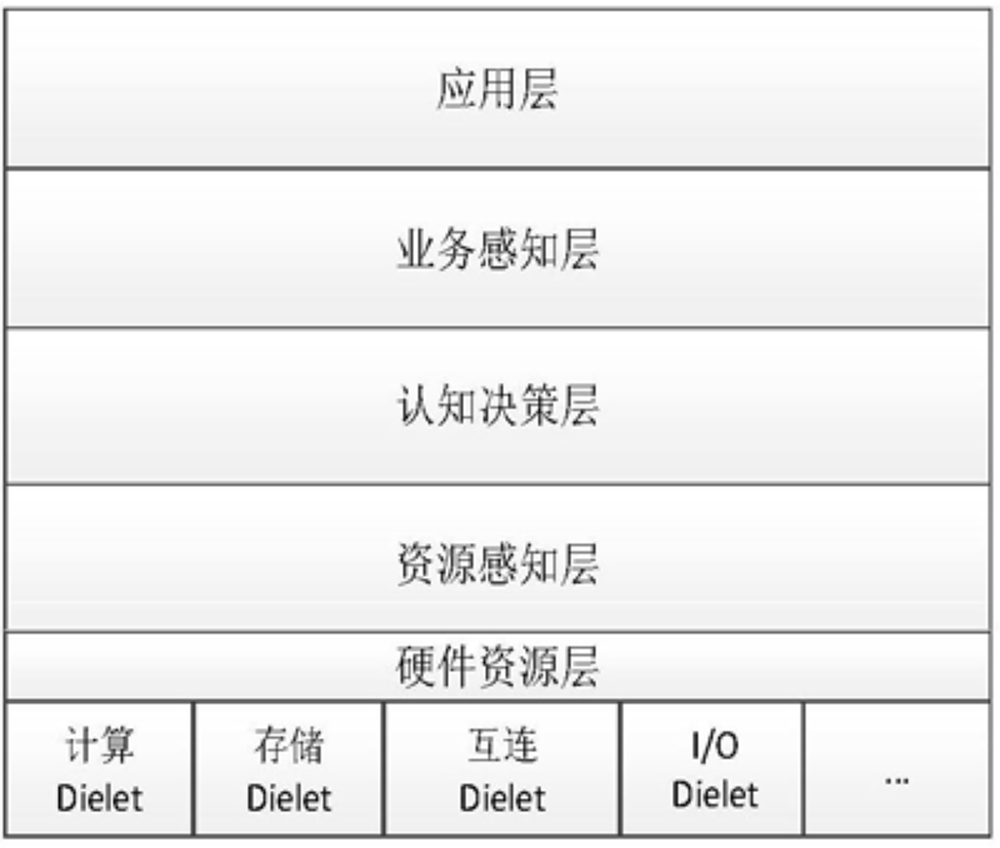

SDSoW采用了一種領域專用軟硬件協同計算架構,結合了擬態計算和軟件定義互連的思想,以綜合發揮芯片技術在新結構、新計算、新互連、新集成上的后發優勢。擬態計算是鄔江興院士首創的一項面向領域的高性能、高效能軟硬件協同領域專用變結構計算體系理論,讓計算結構能主動根據應用需求進行動態重構。據介紹,相較剛性結構計算,變結構計算對計算能效的提升大概在1~3個數量級。整體來看,SDSoW的體系結構有5層,從下到上依次是硬件資源層、資源感知層、認知決策層、業務感知層、應用層。

▲SDSoW體系結構

在硬件資源層,SDSoW借鑒了預制件組裝和晶圓級異構集成等理念,根據不同應用需求,實現不同功能結構(如計算、存儲、互連、IO等)、性能、制程工藝等混合粒度預制件(芯粒,Dielet)的高效集成。具體來說,這個異構系統包含晶圓級互連基板、晶圓級互連基板上的若干芯粒、用于不同芯粒之間互連的軟件定義晶上互連網絡。晶圓級互連基板通過重布線層RDL或光刻方式,提供芯粒之間的互連線路。各芯粒通過TCB(熱壓焊)與基板連接。預制件的互連將遵循統一的物理接口標準和協議規范,通過晶圓級互連基板和軟件定義晶上互連網絡進行數據交換。每個芯粒結構相當于一個“專用FPGA”,根據領域應用功能需求來定制,芯粒結構內的函數化算粒模塊以軟件定義的方式進行不同的組合和功能重建,從而滿足差異化的應用及任務映射需求,實現資源復用。再往上一層是資源感知層,用于通過感知算法獲取硬件資源層各預制件的計算特征及狀態信息,并將資源信息傳遞給認知決策層。業務感知層對目標應用任務進行分解,得到應用任務的計算特征和業務屬性,將業務信息反饋給認知決策層。然后認知決策層依據資源信息、業務信息、調度原則和知識庫進行主動決策,動態構建適用于應用任務需求的計算結構,并將該計算結構作為系統配置,作用于硬件資源層。硬件資源層可基于這些系統配置,重構各個預制件之間的組合關系和互連結構。最后應用層負責提供對各種應用業務的支持。

04.明年落地交換芯片最快兩年打造完整系統

當前SDSoW創新體系結構仍處研發階段,2020年進入加速發展期,之江實驗室已經率先落地了一個先導項目,旨在打通SDSoW的工藝鏈條。據鄔江興院士團隊核心成員透露,按照樂觀估計,如果產業鏈協同順利,最快兩年可打造出完整SDSoW系統,保守3-5年可實現技術突破。已有四五十家科研機構及企業參與推進相關項目的落地,包括之江實驗室、紫金山實驗室、嵩山實驗室、海河實驗室等。明年之江實驗室就會出第一個基于SDSoW工藝流程做出的8T交換芯片,今年一些陸續流片和頂層設計已初步完成。鄔江興院士團隊相信,SDSoW生態發展必須“既不排外,又要有根”,根便是技術創新內核。以Chiplet為例,SDSoW在接口標準上,既與國際Chiplet產業聯盟UCIe兼容,又要高于UCIe標準,通過軟件定義支持面向場景的互連協議與互連網絡屬性,聯合學術界、產業界共同提出中國自主創新、自持發展的SDSoW接口與協議標準,并與國內封裝廠、晶圓廠合作探索Chiplet相關技術成果如何遷移和復用到SDSoW平臺。待相關流程建立起來,SDSoW才會逐漸走向穩定和規模化。當然,在應用驅動時代,SDSoW如想發展起來,離不開強需求的應用場景。

從特性來看,SDSoW技術應用到像大型信息基礎設施這樣的大規模系統能放大其連乘性效益,其軟件定義功能亦有助于具備復雜功能的無人設備靈活配置資源。但對于像桌面端這種對功耗和多芯粒要求并不苛刻的應用,具備成本優勢的SoC(片上系統)仍將長期占據主流。鄔江興院士團隊核心成員預測,等工藝流程充分成熟與規模化,且開發敏捷性和經濟性均優于SoC,SDSoW有可能會在通用桌面等場景替代SoC,屆時將實現全產業突破。未來SDSoW亦有望跟類腦計算等新型計算技術結合,實現一些更泛在的科學及工程創新。他告訴芯東西,未來兩類芯片公司預計最有可能成為SDSoW技術方向的主導者。一類是特色技術明顯的芯片公司。他們本身在SoC領域已有生存空間,既能照常產出物理形態的芯片,也能產出SDSoW標準化芯粒產品。另一類是有強應用場景驅動的大公司。他們足以支持應用級別的系統定義,可基于IDM思路整合各種芯粒和定制晶圓基板,再借助國內系統組裝、供電散熱和一些成熟工具鏈來發展SDSoW系統。整個系統開發、調試、敏捷迭代時間都會大幅縮短,成本投入也將降下來。

05.結語:各立山頭絕非上策形成聚力才能破解困局

受全球經濟復蘇乏力疊加美國出口管制新規對我國半導體產業的阻滯干擾,全球半導體產業分工體系和布局正在發生深刻調整,中國芯片自主發展的前路更加艱難曲折,但不會因為外界的影響而動搖變化。此時好鋼更須用在刀刃上,各立山頭只能在局部場景解決局部問題,只有將中國半導體產業的整體資源形成聚力,打造一個中國集成電路的珠峰,才有可能形成對抗的力量。當前的中國大陸半導體產業,短在先進芯片制造、光刻機等先進設備以及EDA軟件,長在芯片設計創新和封測。鄔江興院士團隊相信,將結構創新與工藝創新結合的SDSoW,有望將我國半導體產業既有優勢協同起來,充分兼顧國內半導體發展水平,趟出一條繞開先進制程等屏障的新路,給國產制造業產能的補位提供緩沖期。國內半導體現有的存量技術和產業裝備,足夠支撐SDSoW形成產業閉環,SDSoW是一個“蹦一蹦就能摸得到的籃圈目標”, 屬于基于國內工藝鏈條和設計流程的摸高式創新,關鍵要看蹦的動力有多大、產業鏈各環節協同有多緊密。在人類已進入大工程科研時代,在我國芯片半導體面臨極端困難的情況下,我們要發揚“聚是一團火、散是滿天星”的精神,盡管SDSoW的前行之路注定崎嶇,但對中國而言,卻是為數不多可自持發展的“光明之路”,也是我們這個時代的中國半導體人必須要走好的自立自強之路。團結一切可以團結的力量、聚集一切可以聚集的資源,一定能早日開創我國半導體的嶄新局面。SDSoW更多技術細節和專利開放情況,敬請關注將在12月10日舉辦的第五屆軟件定義晶上系統技術與產業聯盟大會。

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。