芯片中的CP是什么CP

芯片中的CP一般指的是CP測試,也就是晶圓測試(Chip Probing)。

一、CP測試是什么

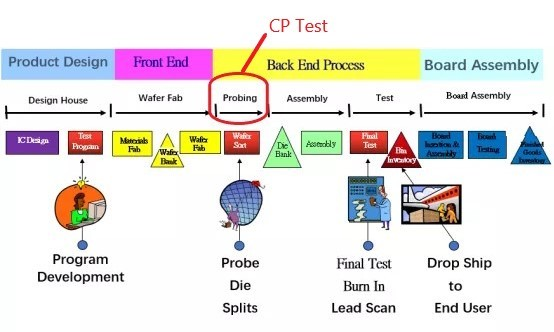

CP測試在整個芯片制作流程中處于晶圓制造和封裝之間,測試對象是針對整片晶圓(Wafer)中的每一個Die,目的是確保整片(Wafer)中的每一個Die都能基本滿足器件的特征或者設計規格書,通常包括電壓、電流、時序和功能的驗證。

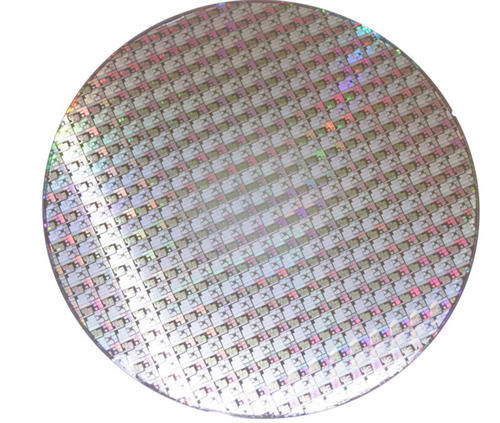

CP測試的具體操作是在晶圓制作完成之后,成千上萬的裸DIE(未封裝的芯片)規則的分布滿整個Wafer。由于尚未進行劃片封裝,只需要將這些裸露在外的芯片管腳,通過探針(Probe)與測試機臺(Tester)連接,進行芯片測試就是CP測試。

圖 1 CP Test在芯片產業價值鏈上的位置

二、為什么要做CP測試

因為通常在芯片封裝階段時,有些管腳會被封裝在芯片內部,導致有些功能無法在封裝后進行測試,因此Wafer中進行CP測試最為合適。

圖 2 Wafer上規則的排列著DIE

而且Wafer制作完成之后,由于工藝偏差、設備故障等原因引起的制造缺陷,分布在Wafer上的裸DIE中會有一定量的殘次品。CP測試的目的就是在封裝前將這些殘次品找出來(Wafer Sort),同時還可以避免被封裝后無法測試芯片性能,優化生產流程,簡化步驟,同時提高出廠的良品率,縮減后續封裝測試的成本。

另外,有些公司會根據CP測試的結果,將芯片劃分等級,將這些產品投入不同的市場,購買者需要注意這一點。

三、測試內容有哪些

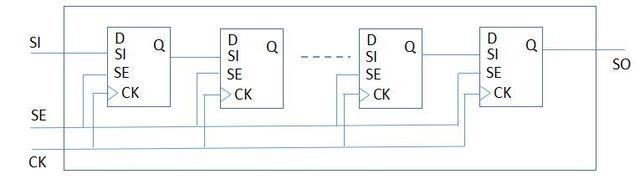

1、SCAN

SCAN用于檢測芯片邏輯功能是否正確。DFT設計時,先使用DesignCompiler插入ScanChain,再利用ATPG(Automatic Test Pattern Generation)自動生成SCAN測試向量。SCAN測試時,先進入Scan Shift模式,ATE將pattern加載到寄存器上,再通過Scan Capture模式,將結果捕捉。再進入下次Shift模式時,將結果輸出到ATE進行比較。

圖 3 Scan Chain示意圖

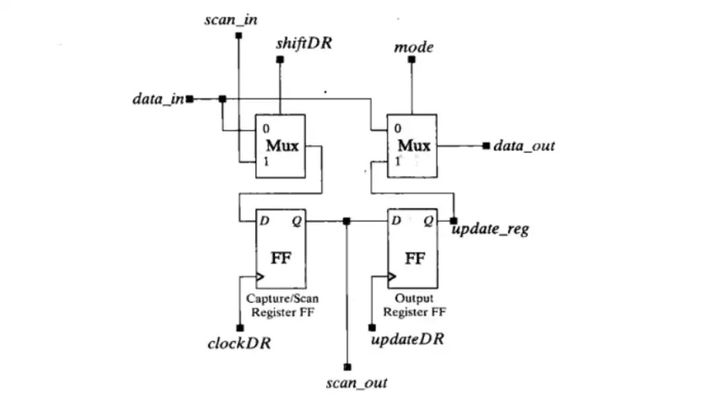

2、Boundary SCAN

Boundary SCAN用于檢測芯片管腳功能是否正確。與SCAN類似,Boundary SCAN通過在IO管腳間插入邊界寄存器(Boundary Register),使用JTAG接口來控制,監測管腳的輸入輸入出狀態。

圖 4 Boundary Scan原理圖

四、測試方法有哪些

1、DC/AC Test

DC測試包括芯片Signal PIN的Open/Short測試,電源PIN的PowerShort測試,以及檢測芯片直流電流和電壓參數是否符合設計規格。AC測試檢測芯片交流信號質量和時序參數是否符合設計規格。

2、RF Test

對于無線通信芯片,RF的功能和性能至關重要。CP中對RF測試來檢測RF模塊邏輯功能是否正確。

3、存儲器

存儲器測試數量較大,因為芯片往往集成著各種類型的存儲器(例如ROM/RAM/Flash),為了測試存儲器讀寫和存儲功能,通常在設計時提前加入BIST(Built-In SelfTest)邏輯,用于存儲器自測。芯片通過特殊的管腳配置進入各類BIST功能,完成自測試后BIST模塊將測試結果反饋給Tester。

(1)ROM(Read-Only Memory)通過讀取數據進行CRC校驗來檢測存儲內容是否正確。

(2)RAM(Random-Access Memory)通過除檢測讀寫和存儲功能外,有些測試還覆蓋DeepSleep的Retention功能和Margin Write/Read等等。

(3)Embedded Flash除了正常讀寫和存儲功能外,還要測試擦除功能。

(4)Wafer還需要經過Baking烘烤和Stress加壓來檢測Flash的Retention是否正常。

(5)還有Margin Write/Read、Punch Through測試等等。

4、其他Function Test

芯片其他功能測試,用于檢測芯片其他重要的功能和性能是否符合設計規格。

隨著芯片工藝越來越先進,晶體管密度越來越高,芯片測試的復雜度和難度也成倍地增長。本文金譽半導體只梳理了一些梳理基本的測試概念,和簡單基礎的CP測試知識,后續我們會再針對這個話題進行一些更加全面的探討。

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。

pa相關文章:pa是什么

路由器相關文章:路由器工作原理

路由器相關文章:路由器工作原理